Altera ALTDQ_DQS2 User Manual

Page 66

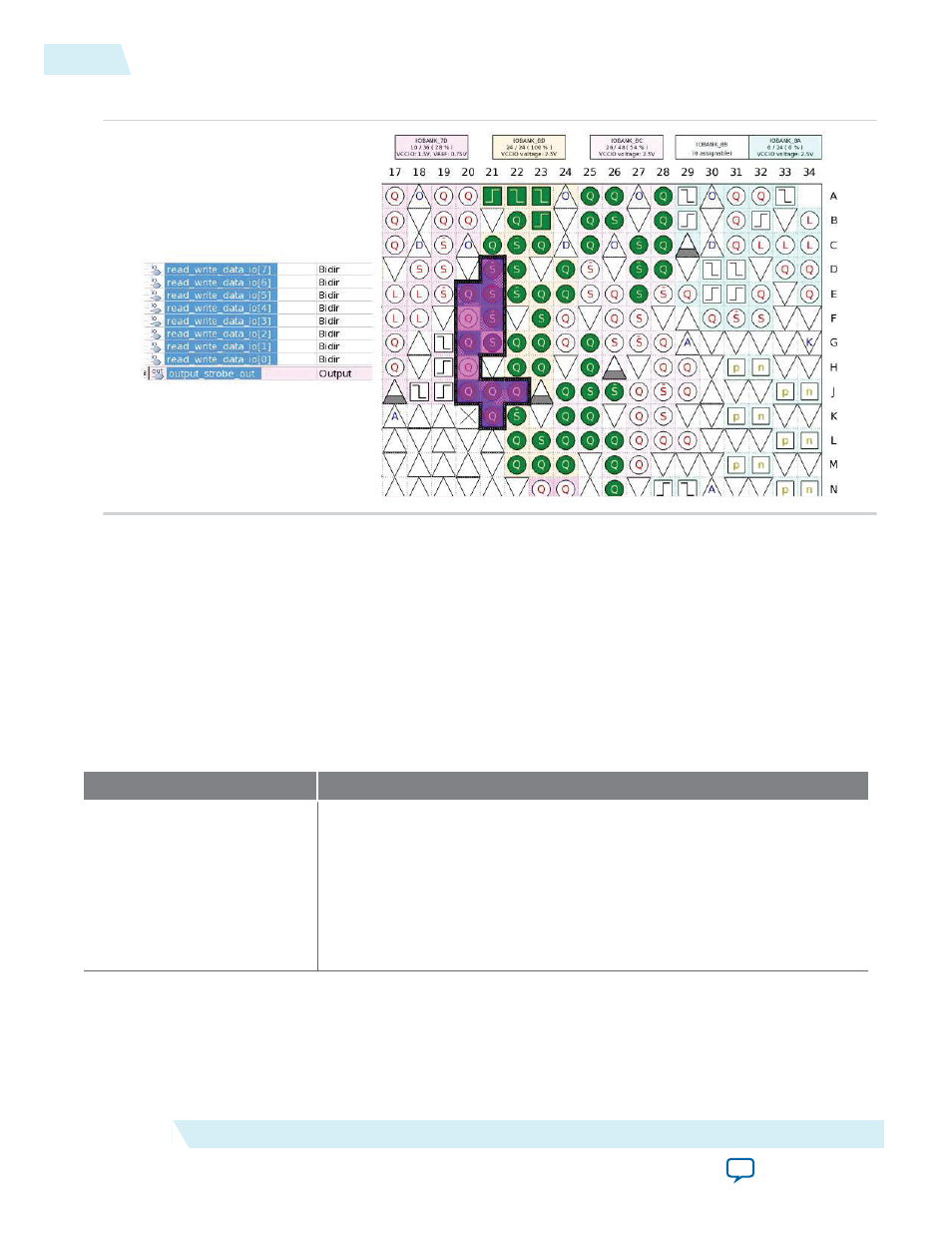

Figure 30: Pin Planner

10.Run the Fitter, Timing Analysis, and Assembler. An SDC example (top.sdc) is included in the example

design.

Related Information

•

Understanding Simulation Results—Stratix V Design Example

Understanding Simulation Results—Stratix V Design Example

ln the Stratix V design example, a generic testbench is used to test the write and read operations in the

ALTDQ_DQS2 IP core. The following table lists the components in the testbench.

Table 21: Testbench Components

Component

Description

DQS Driver

• Acts as a host controller, sends read/write commands to the ALTDQ_

DQS2 IP core.

• Compares data read back from a DQS agent to what it should be.

• Has a side channel (side reads/writes) communicating directly with the

DQS agent, bypassing the ALTDQ_DQS2 IP core. Use the data in the

side reads/writes to compare with the data sent to or received from the

ALTDQ_DQS2 IP core.

66

Understanding Simulation Results—Stratix V Design Example

UG-01089

2014.12.17

Altera Corporation

ALTDQ_DQS2 IP Core User Guide