Altera ALTDQ_DQS2 User Manual

Page 85

Component

Description

DQS Agent

• Acts as an external memory device.

• Has a side channel (side reads/writes) communicating directly with the

DQS Driver, bypassing the ALTDQ_DQS2 IP core. Use the data in the

side reads/writes to compare with the data sent to or received from the

ALTDQ_DQS2 IP core.

Note: Random data is generated and used in the testbench. You may see other data values if you are using

different operating system and seeds.

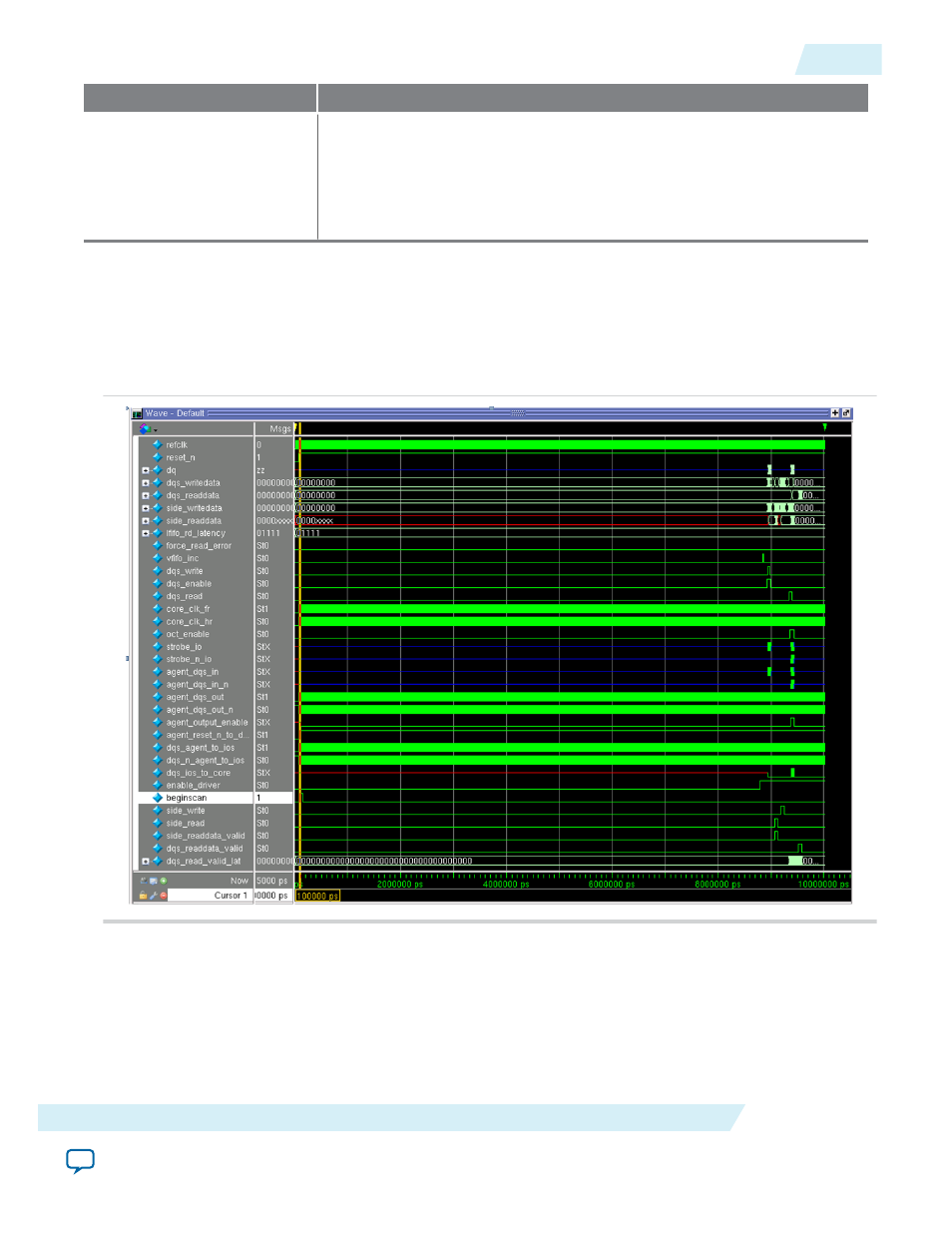

The following figure shows the waveform for the testbench generated after executing the

top_run_msim_rtl_verilog.do file.

Figure 55: Example Waveform

All ports are in reset mode until the

reset_n

signal is asserted at 70 ns. Then, the

core_clk_fr

and

core_clk_hr

clocks start to toggle. The

agent_reset_n_to_dqs

signal is asserted at 95 ns to reset the

ALTDQ_DQS2 IP core located in top_inst.

UG-01089

2014.12.17

Understanding Simulation Results—Arria V Design Example

85

ALTDQ_DQS2 IP Core User Guide

Altera Corporation