Sopc builder tutorial, Software requirements, Verifying avalon-mm slave dut – Altera Avalon Verification IP Suite User Manual

Page 157: Chapter 1. sopc builder tutorial

May 2011

Altera Corporation

Avalon Verification IP Suite User Guide

1. SOPC Builder Tutorial

This chapter demonstrates how to use the Avalon-MM Master and Slave BFMs to

verify Avalon-MM master and slave components in an SOPC Builder design. In the

first example, the DUT is an on-chip RAM that includes an Avalon-MM slave port. Its

behavior is verified using the Avalon-MM Master BFM component. The second

example verifies an Avalon-MM master DUT using the Avalon-MM Slave BFM

component.

Software Requirements

The following software and file are required to run the test:

■

Quartus II software, version 11.0 or later.

■

ModelSim-AE software that you installed with the Quartus II software.

■

The ug_avalon_verification.zip file. This design example file is available for

.

Verifying Avalon-MM Slave DUT

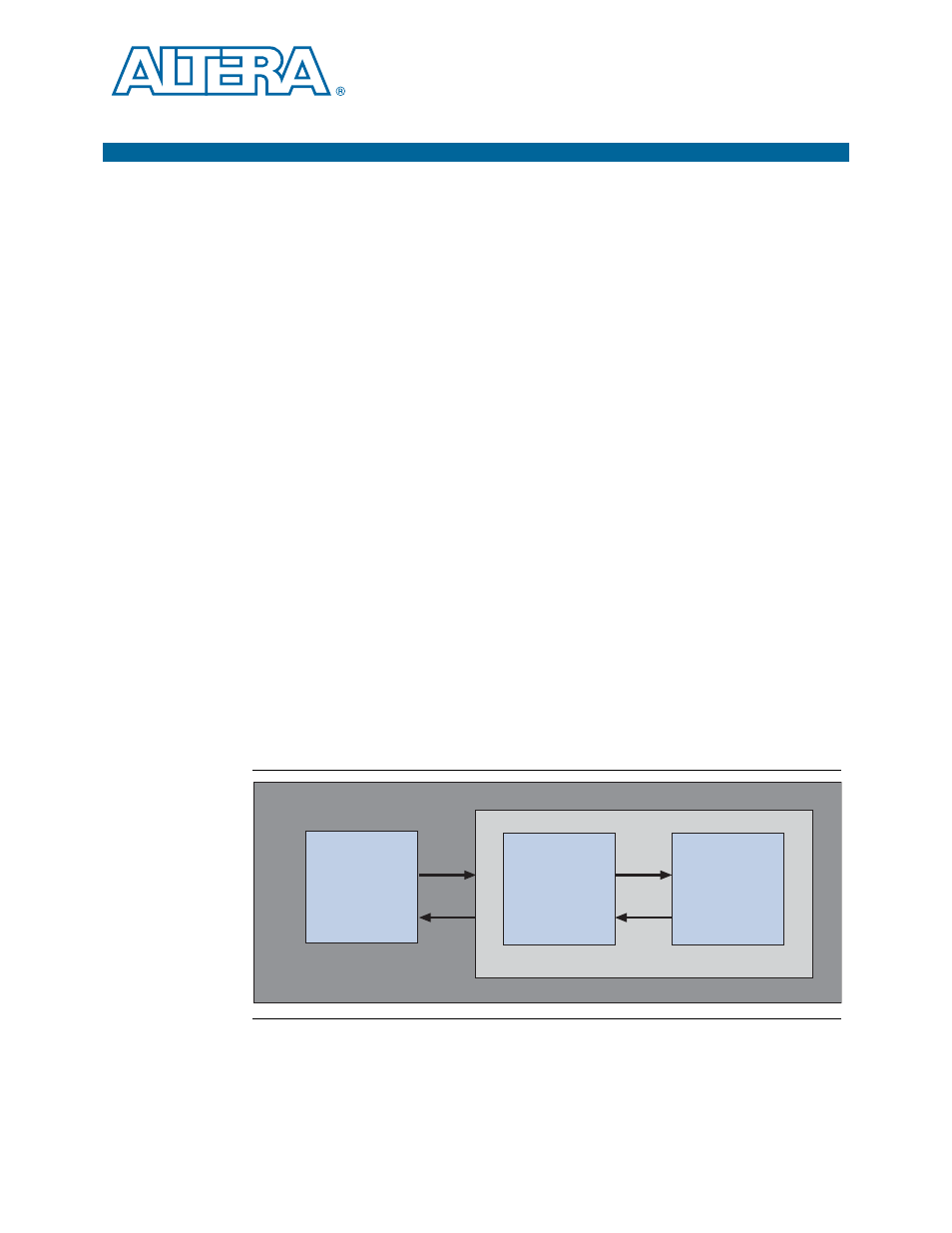

illustrates the top-level testbench to verify an Avalon-MM slave

component. An on-chip RAM component is connected to the Avalon-MM Master

BFM in SOPC Builder. The test program initializes the Avalon-MM Master BFM. After

the initialization and system reset are completed, the test program instructs the

master BFM to write random data to the slave DUT. The write data is also saved into a

local array for future reference. The Avalon-MM Master BFM reads back the data

written, compares it to the data stored in the local array, and reports mismatches. The

test passes if all the read data is correct.

Figure 1–1. Top-Level Testbench for an Avalon-MM Slave Component

On-Chip RAM

Avalon-MM

Slave

Avalon-MM

Master

BFM

SOPC Builder

Top-level File

Test

Prorgam