Timing, Timing –2 – Altera Avalon Verification IP Suite User Manual

Page 91

1–2

Chapter 1: Avalon-ST Source BFM

Functional Description

Avalon Verification IP Suite User Guide

May 2011

Altera Corporation

Timing

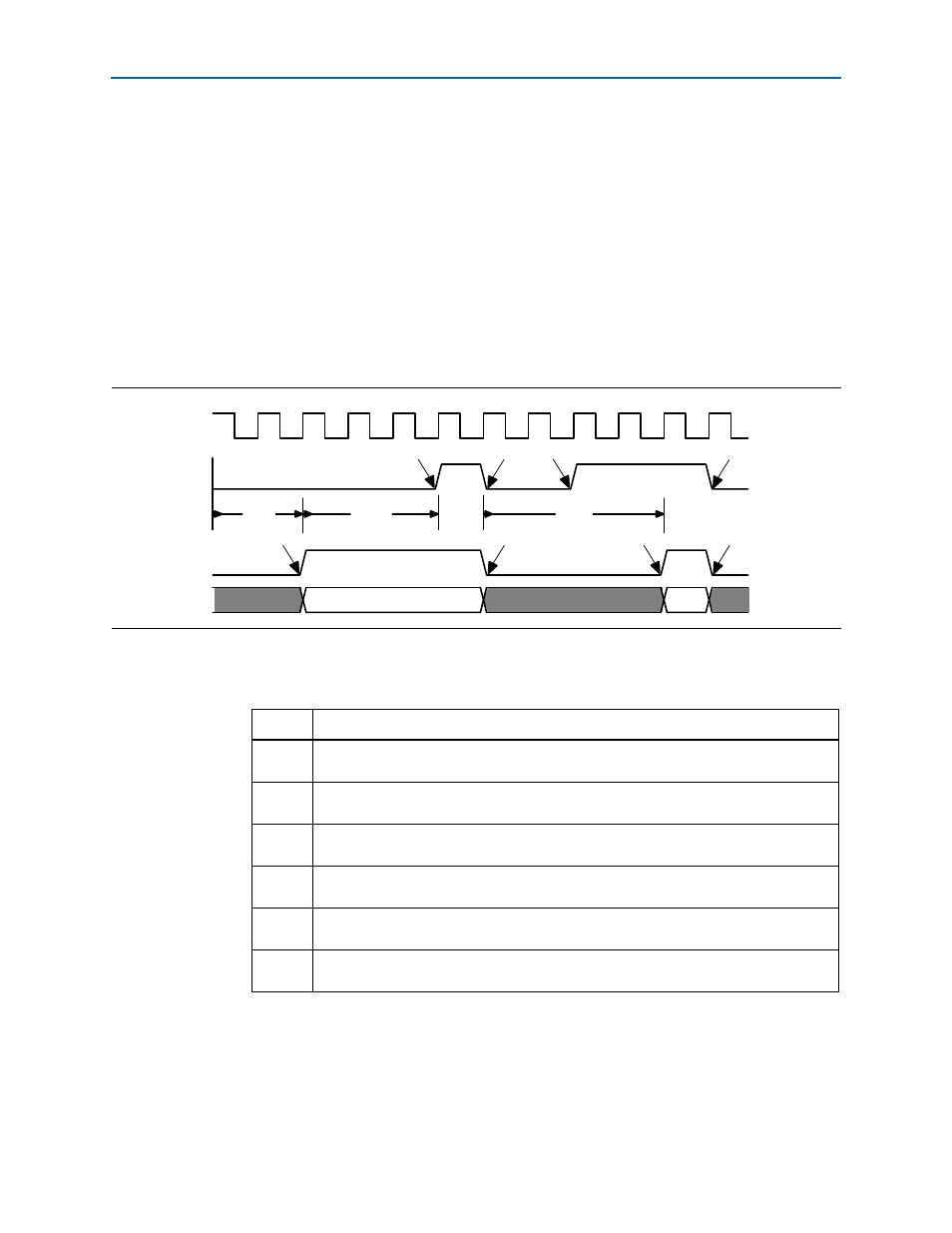

The timing diagram shown in

illustrates the timing for an Avalon-ST

Source BFM sending data to a sink. In the first instance the sink is not ready when the

source has data. In the second instance, the sink is ready but the source does not

initially have valid data.

1

The Avalon-ST BFM behaves differently depending on whether the sink’s

READY_LATENCY = 0

or

READY_LATENCY > 0

. When the ready latency is 0, the source

BFM holds its current transaction until the sink is ready. When the ready latency is

greater than 0, the BFM drives idles until the sink is ready, then it drives the

transaction.

illustrates the timing when

READY_LATENCY = 0

.

explains the annotations used in

.

Figure 1–2. Avalon-ST Source Sending Data to a Sink

CLK

ready

valid

data

D1

D2

S

src_dr

S

src_dr

S

src_rdy

S

tc

S

src_~rdy

S

src_~rdy

S

tc

S

src_rdy

T

idle

T

idle

T

rl_1

Table 1–1. Key to Annotations in

Symbol

Description

T

idle

The idle time before a transactions. This time is set by the command

set_transaction_idles

.

T

rl_1

The response latency for the first source to sink transaction, which is three cycles. The

source gets this time using the

get_response_latency

command.

S

src_dr

Signals that the source is driving valid data. The event name is

signal_src_driving_transaction

.

S

src_rdy

Signals the source has received the assertion of

ready

from the sink. The event name is

signal_src_ready

.

S

tc

Signals the first transaction is complete. The event name is

signal_src_transaction_complete

.

S

src_~rdy

Signals the source has received the deassertion of

ready

from the sink. The event name

is

signal_src_not_ready

.