Slave_ready_delay_mode, Example 6-15. set_wr_resp_valid_delay(), Variable to configure the beha – Altera Mentor Verification IP Altera Edition AMBA AXI4-Lite User Manual

Page 127: Point of the delay is determined by the, E delay is determined by the

SystemVerilog Tutorials

Verifying a Master DUT

Mentor Verification IP AE AXI4-Lite User Guide, V10.3

127

April 2014

shows the BVALID signal delay set to two ACLK cycles. You can edit this

function to change the BVALID signal delay.

Example 6-15. set_wr_resp_valid_delay()

// Function : set_wr_resp_valid_delay

// This is used to set write response phase valid delay to start

// driving write response phase after specified delay.

function void set_wr_resp_valid_delay(axi4_transaction trans);

trans.set_write_response_valid_delay(2);

endfunction

slave_ready_delay_mode

The slave_ready_delay_mode variable holds the configuration that defines the starting point of

any delay applied to the *READY signals. You can configure it to the enumerated type values

of AXI4_VALID2READY (default) or AXI4_TRANS2READY.

The default configuration (slave_ready_delay_mode = AXI4_VALID2READY) corresponds to

the delay measured from the positive edge of ACLK when *VALID is asserted.

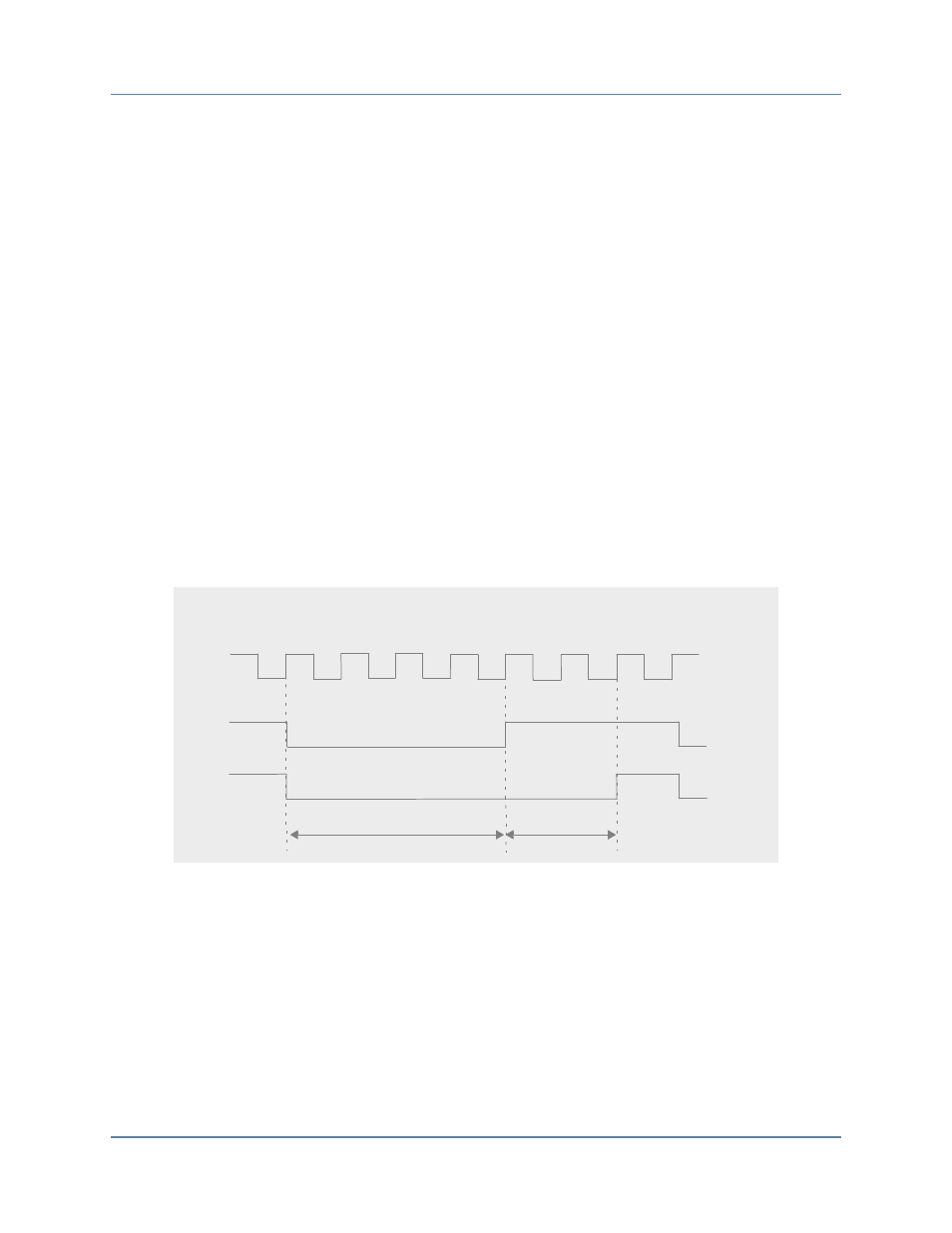

shows how to achieve a *VALID before *READY handshake.

Figure 6-5. slave_ready_delay_mode = AXI4_VALID2READY

The nondefault configuration (slave_ready_delay_mode = AXI4_TRANS2READY) corresponds

to the delay measured from the completion of a previous transaction phase (*VALID and

*READY both asserted).

shows how to achieve a *READY before *VALID

handshake.

*VALID

*READY

ACLK

*_valid_delay = 4

*_ready_delay = 2