Using the basic slave test program api, Example 6-16. slave_ready_delay_mode, Ready both asserted) – Altera Mentor Verification IP Altera Edition AMBA AXI4-Lite User Manual

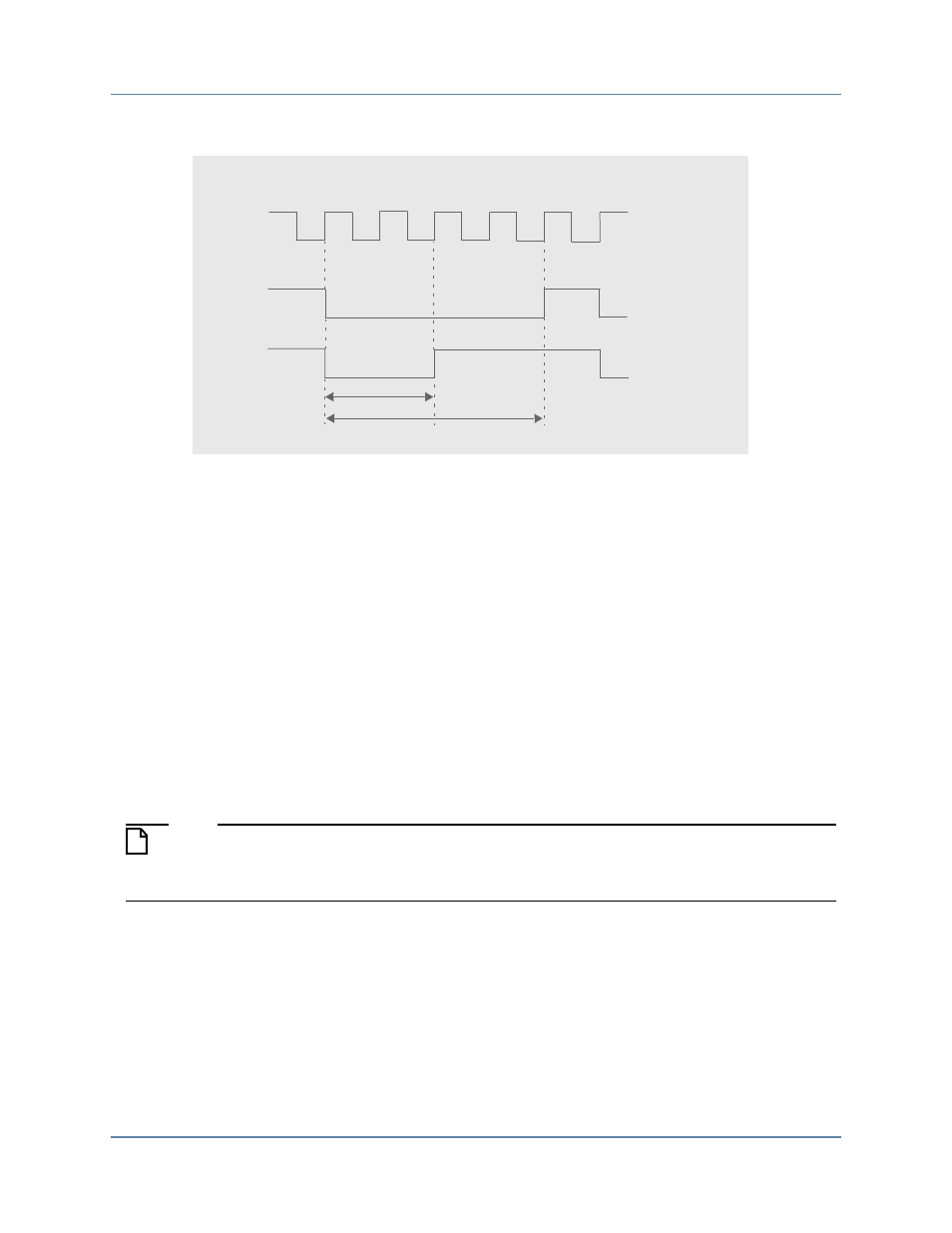

Page 128: Figure 6-6, Shows how to achieve a *ready before *valid

Mentor Verification IP AE AXI4-Lite User Guide, V10.3

128

SystemVerilog Tutorials

Verifying a Master DUT

April 2014

Figure 6-6. slave_ready_delay_mode = AXI4_TRANS2READY

shows the configuration of the slave_ready_delay_mode to its default value.

Example 6-16. slave_ready_delay_mode

// Enum type for slave ready delay mode

// AXI4_VALID2READY - Ready delay for a phase will be applied from

// start of phase (Means from when VALID is asserted).

// AXI4_TRANS2READY - Ready delay will be applied from the end of

// previous phase. This might result in ready before

valid.

typedef enum bit

{

AXI4_VALID2READY = 1'b0,

AXI4_TRANS2READY = 1'b1

} axi4_slave_ready_delay_mode_e;

// Slave ready delay mode seclection : default it is AXI4_VALID2READY

axi4_slave_ready_delay_mode_e slave_ready_delay_mode = AXI4_VALID2READY;

Note

In addition to the previous variables and procedures, you can configure other aspects of

the AXI4-Lite Slave BFM by using the procedures

Using the Basic Slave Test Program API

There are a set of tasks and functions that you can use to create stimulus scenarios based on a

memory-model slave with a minimal amount of editing, as described in the

section.

Consider the following configurations when using the slave test program.

*VALID

*READY

ACLK

*_valid_delay = 4

*_ready_delay = 2