Altera Parallel Flash Loader IP User Manual

Page 42

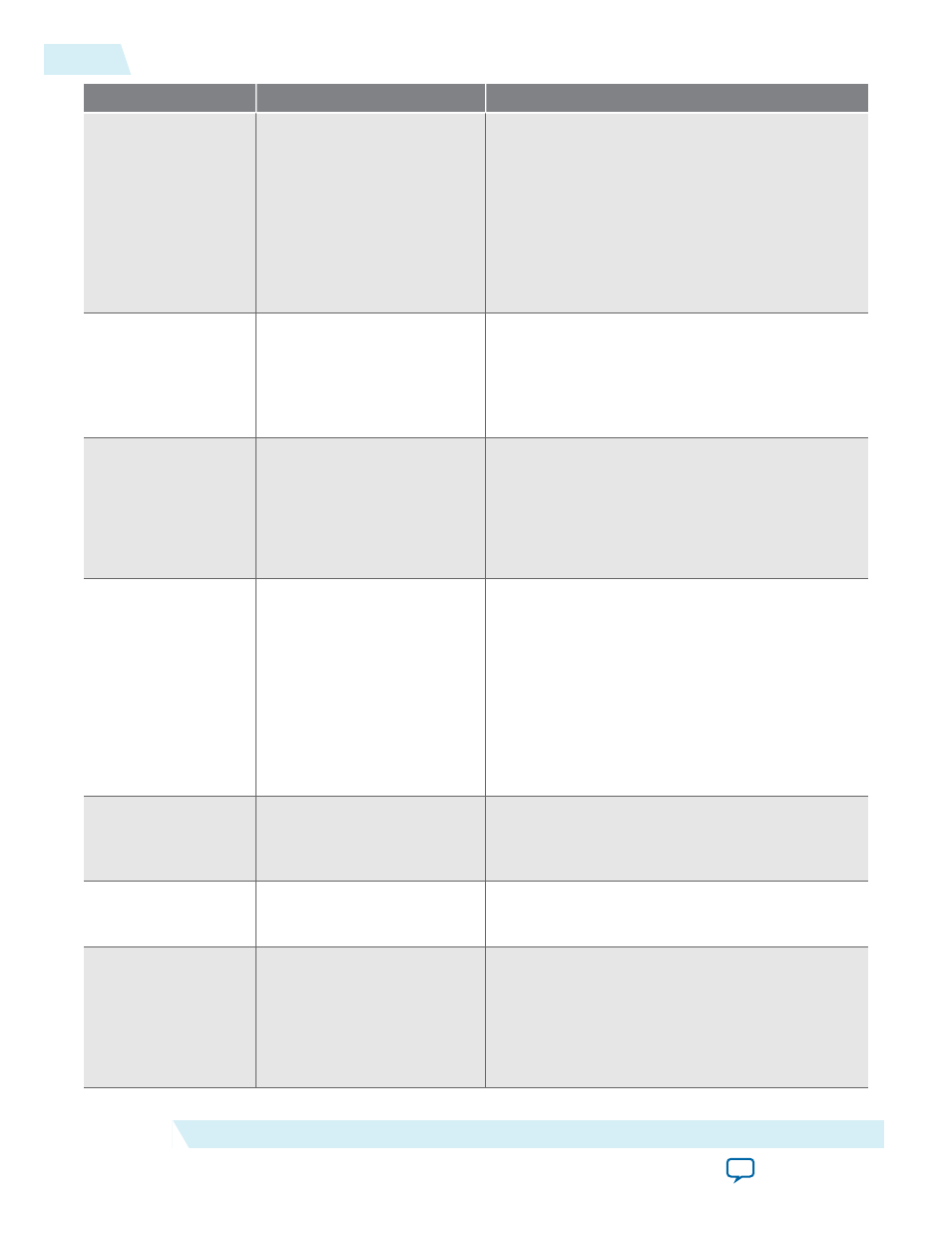

Options

Value

Description

Flash access time

—

Specifies the access time of the flash. You can get

the maximum access time that a flash memory

device requires from the flash datasheet. Altera

recommends specifying a flash access time that is

the same as or longer than the required time.

For CFI parallel flash, the unit is in ns and for

NAND flash, the unit is in us. NAND flash uses

page instead of byte, and requires more access

time. This option is disabled for quad SPI flash.

Option bits byte

address

—

Specifies the start address in which the option bits

are stored in the flash memory. The start address

must reside on an 8-KB boundary.

See related for more information about option

bits.

FPGA configura‐

tion scheme

• PS

• FPP

• FPP ×16 (for Stratix V

devices)

• FPP ×32(for Stratix V

devices)

Select the FPGA configuration scheme. The

default FPP is FPP ×8. If you are using Stratix V

devices, two additional FPP mode is available: FPP

×16 and FPP ×32.

Configuration

failure response

options

Halt, Retry same page, or Retry

from fixed address

Configuration behavior after configuration failure.

• If you select Halt, the FPGA configuration

stops completely after failure.

• If you select Retry same page, after failure, the

PFL IP core reconfigures the FPGA with data

from the same page of the failure.

• If you select Retry from fixed address, the PFL

IP core reconfigures the FPGA with data from

a fixed address in the next option field after

failure.

Byte address to

retry from on

configuration

failure

—

If you select Retry from fixed address for configu‐

ration failure option, this option specifies the flash

address for the PFL IP core to read from the

reconfiguration for a configuration failure.

Include input to

force reconfigura‐

tion

On or Off

Includes an optional reconfiguration input pin

(

pfl_nreconfigure

) to enable a reconfiguration

of the FPGA.

Watchdog timer

On or Off

Enables a watchdog timer for remote system

upgrade support. Turning on this option enables

the

pfl_reset_watchdog

input pin and

pfl_

watchdog_error

output pin, and specifies the

time period before the watchdog timer times out.

This watchdog timer is a time counter which runs

at the

pfl_clk frequency

.

42

Parameters

UG-01082

2015.01.23

Altera Corporation

Parallel Flash Loader IP Core User Guide