Altera Stratix IV E FPGA User Manual

Page 28

6–2

Chapter 6: Board Test System

Stratix IV E FPGA Development Kit User Guide

June 2011

Altera Corporation

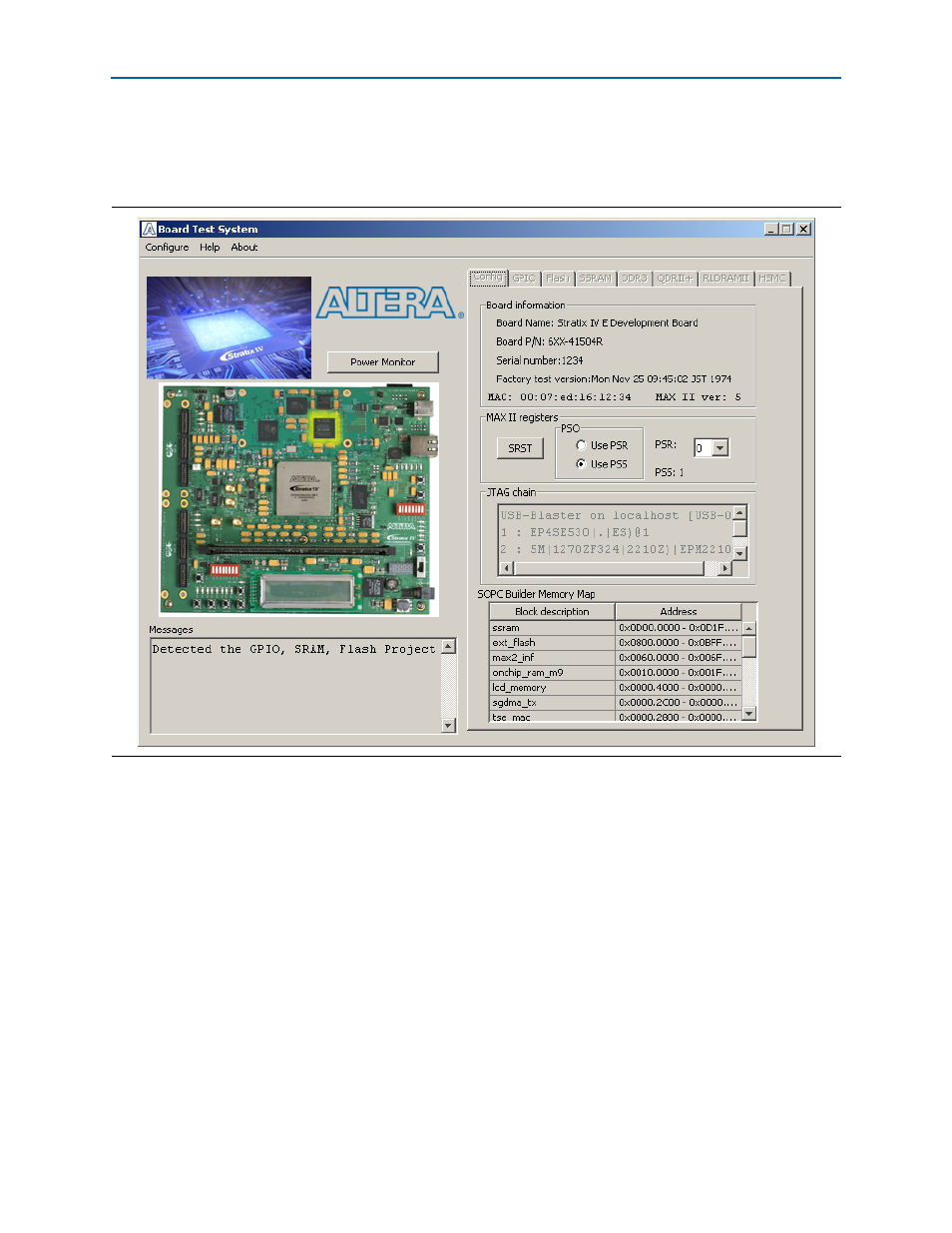

The Board Test System GUI communicates over the JTAG bus to a test design running

in the Stratix IV E device.

shows the initial GUI for a board that is in the

factory configuration.

Several designs are provided to test the major board features. Each design provides

data for one or more tabs in the application. The Configure menu identifies the

appropriate design to download to the FPGA for each tab.

After successful FPGA configuration, the appropriate tab appears and allows you to

exercise the related board features. Highlights appear in the board picture around the

corresponding components.

The Power Monitor button starts the Power Monitor application that measures and

reports current power and temperature information for the board. Because the

application communicates over the JTAG bus to the MAX II device, you can measure

the power of any design in the FPGA, including your own designs.

Figure 6–1. Board Test System Graphical User Interface