Altera Stratix IV GX FPGA Development Board User Manual

Page 16

2–8

Chapter 2: Board Components

MAX II CPLD EPM2210 System Controller

Stratix IV GX FPGA Development Board, 530 Edition Reference Manual

November 2010

Altera Corporation

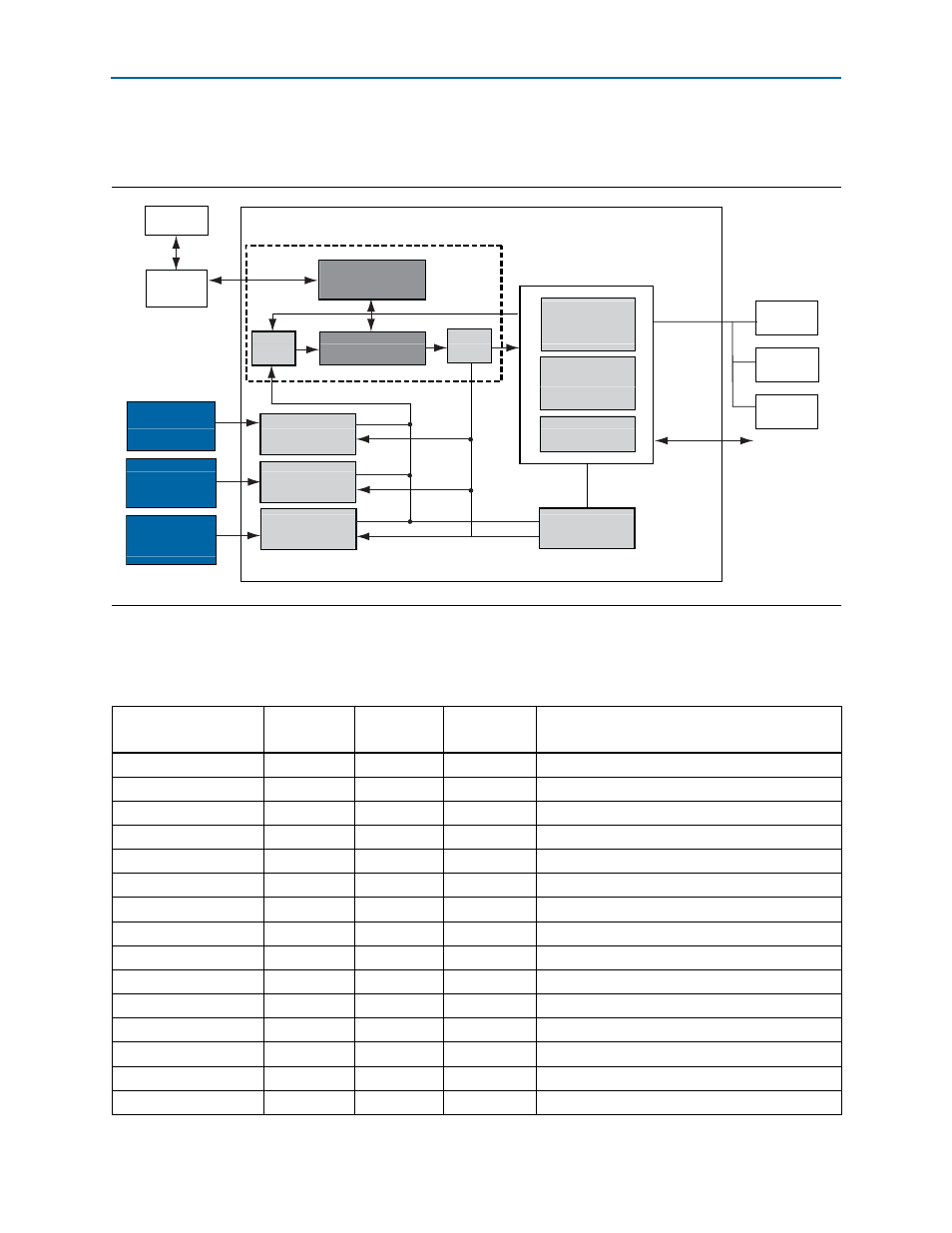

illustrates the MAX II CPLD EPM2210 System Controller's functionality

and external circuit connections as a block diagram.

Table 2–6

lists the I/O signals present on the MAX

II CPLD EPM2210 System

Controller. The signal names and functions are relative to the MAX

II device (U30).

Figure 2–3. MAX II CPLD EPM2210 System Controller Block Diagram

MAX1619

Controller

Information

Register

EMB

Blaster

MAX II Device

Si570

Controller

SLD-HUB

PFL

FSM BUS

Power

Measure

Results

Virtual-JTAG

PC

Temperature

Measure

Results

FPGA

LTC2418

Controller

FLASH

Decoder

Encoder

GPIO

JTAG Control

SRAM

Control

Register

Fast Configuration

Downloader

Si570

Programmable

Oscillator

Table 2–6. MAX II CPLD EPM2210 System Controller Device Pin-Out (Part 1 of 4)

Schematic Signal

Name

I/O Standard

EPM2210

Pin Number

EP4SGX230

Pin Number

Description

FSM_A25

2.5-V

D5

AP30

FSM bus address

FSM_A24

2.5-V

B1

AN30

FSM bus address

FSM_A23

2.5-V

D4

AL31

FSM bus address

FSM_A22

2.5-V

B9

AK31

FSM bus address

FSM_A21

2.5-V

D9

AR32

FSM bus address

FSM_A20

2.5-V

A10

AP32

FSM bus address

FSM_A19

2.5-V

C9

AH29

FSM bus address

FSM_A18

2.5-V

B10

AG29

FSM bus address

FSM_A17

2.5-V

A11

AR35

FSM bus address

FSM_A16

2.5-V

E10

AP35

FSM bus address

FSM_A15

2.5-V

B11

AL32

FSM bus address

FSM_A14

2.5-V

D10

AK32

FSM bus address

FSM_A13

2.5-V

A12

AU33

FSM bus address

FSM_A12

2.5-V

C10

AT33

FSM bus address

FSM_A11

2.5-V

B12

AH30

FSM bus address