Ddr sdram chip (u63), Ddr sdram chip (u63) –9 – Altera Nios Development Board Stratix II Edition User Manual

Page 19

Altera Corporation

Reference Manual

2–9

May 2007

Nios Development Board Stratix II Edition

Board Components

The following pins on U74 have fixed connections, which restricts the

usable modes of operation:

■

MODE is pulled low to enable Linear Burst

■

ZZ is pulled low to leave the chip enabled

■

GLOBALW_n is pulled high to disable the global write.This is the

default behavior for GLOBALW_n that can be changed.

■

CE2 and CE3_n are wired high and low respectively to be enabled

and to make CE1_n the master chip enable.This is the default

behavior for GLOBALW_n that can be changed.

f

See www.cypress.com for detailed information about the SSRAM chip.

DDR SDRAM

Chip (U63)

U63 is a Micron DDR SDRAM chip. The part number is MT46V16M16P-

6T. The DDR SDRAM pins are connected to the FPGA as shown in

. Altera provides a DDR SDRAM controller that allows a Nios II

processor to access the DDR SDRAM device as a large, linearly-

addressable memory.

G18

88

GW_n

ssram_gw_n

A12

89

CLK

sram_clk

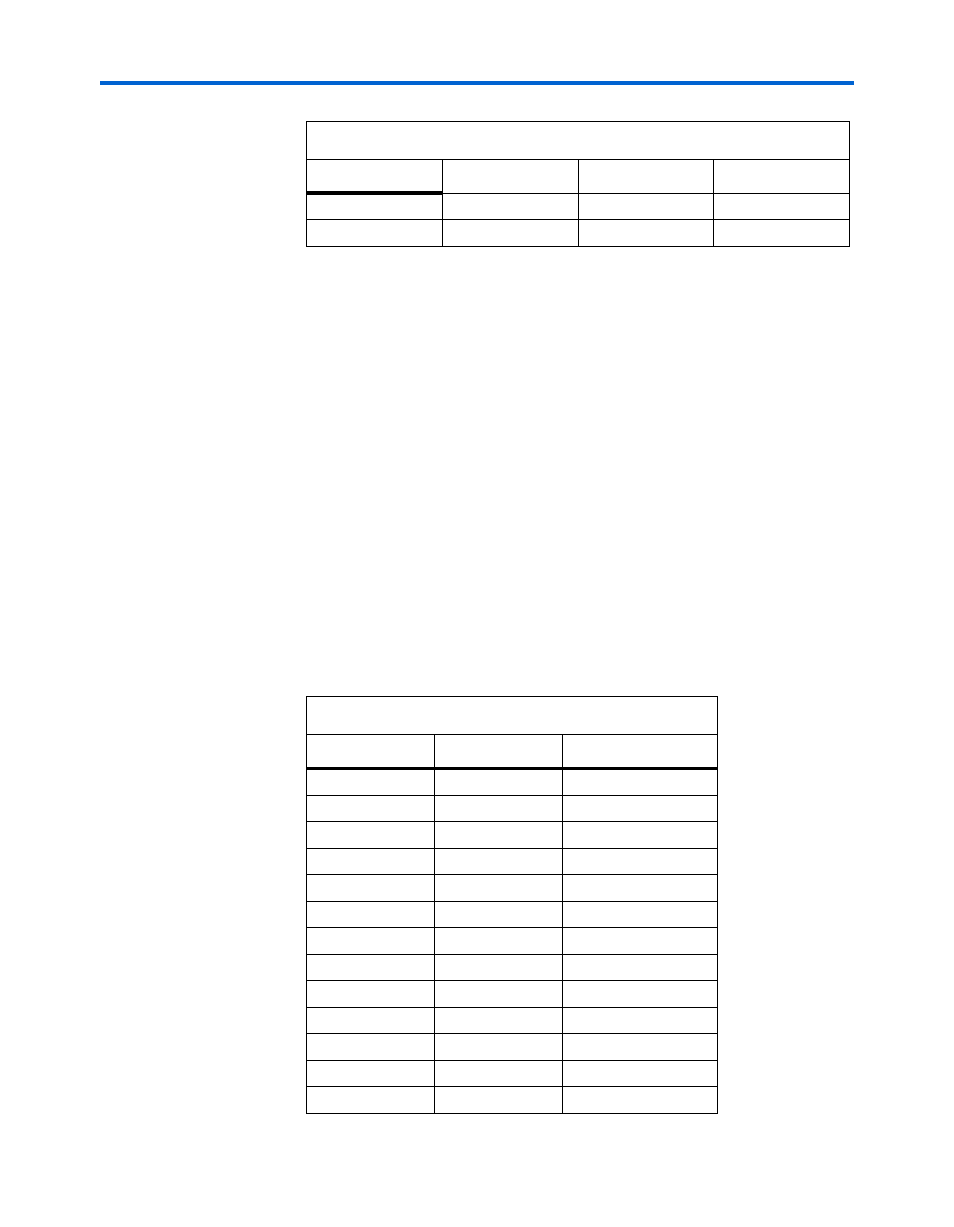

Table 2–6. SSRAM Pin Table (Continued)

FPGA Pin

U74 Pin

Pin Function Board

Net

Name

Table 2–7. DDR SDRAM Pin Table

FPGA Pin

U63 Pin

Board Net Name

DD9

2

sdram_dq0

D8

4

sdram_dq1

C8

5

sdram_dq2

A9

7

sdram_dq3

B11

8

sdram_dq4

C11

10

sdram_dq5

A10

11

sdram_dq6

D10

13

sdram_dq7

A5

54

sdram_dq8

B5

56

sdram_dq9

D6

57

sdram_dq10

A6

59

sdram_dq11

A8

60

sdram_dq12