Serial connector (j19), Serial connector (j19) –15 – Altera Nios Development Board Stratix II Edition User Manual

Page 25

Altera Corporation

Reference Manual

2–15

May 2007

Nios Development Board Stratix II Edition

Board Components

f

See www.smsc.com for detailed information about the LAN91C111

device.

Serial Connector

(J19)

J19 is a standard DB-9 serial connector. It is typically used for

communication between the FPGA and a host computer via an RS-232

serial cable. Level-shifting buffer (U52) is used between J19 and the FPGA

because the FPGA device cannot interface to RS-232 voltage levels

directly.

N21

70

Data Line

fe_d13

M22

69

Data Line

fe_d14

M21

68

Data Line

fe_d15

M24

66

Data Line

fe_d16

M23

65

Data Line

fe_d17

L19

64

Data Line

fe_d18

L18

63

Data Line

fe_d19

L21

61

Data Line

fe_d20

L20

60

Data Line

fe_d21

L23

59

Data Line

fe_d22

L22

58

Data Line

fe_d23

K20

56

Data Line

fe_d24

K19

55

Data Line

fe_d25

K22

54

Data Line

fe_d26

K21

53

Data Line

fe_d27

J20

51

Data Line

fe_d28

J19

50

Data Line

fe_d29

J22

49

Data Line

fe_d30

J21

48

Data Line

fe_d31

Note to

:

(1)

Nets fe_a0 and fe_a16 to fe_a23 do not connect to U4.

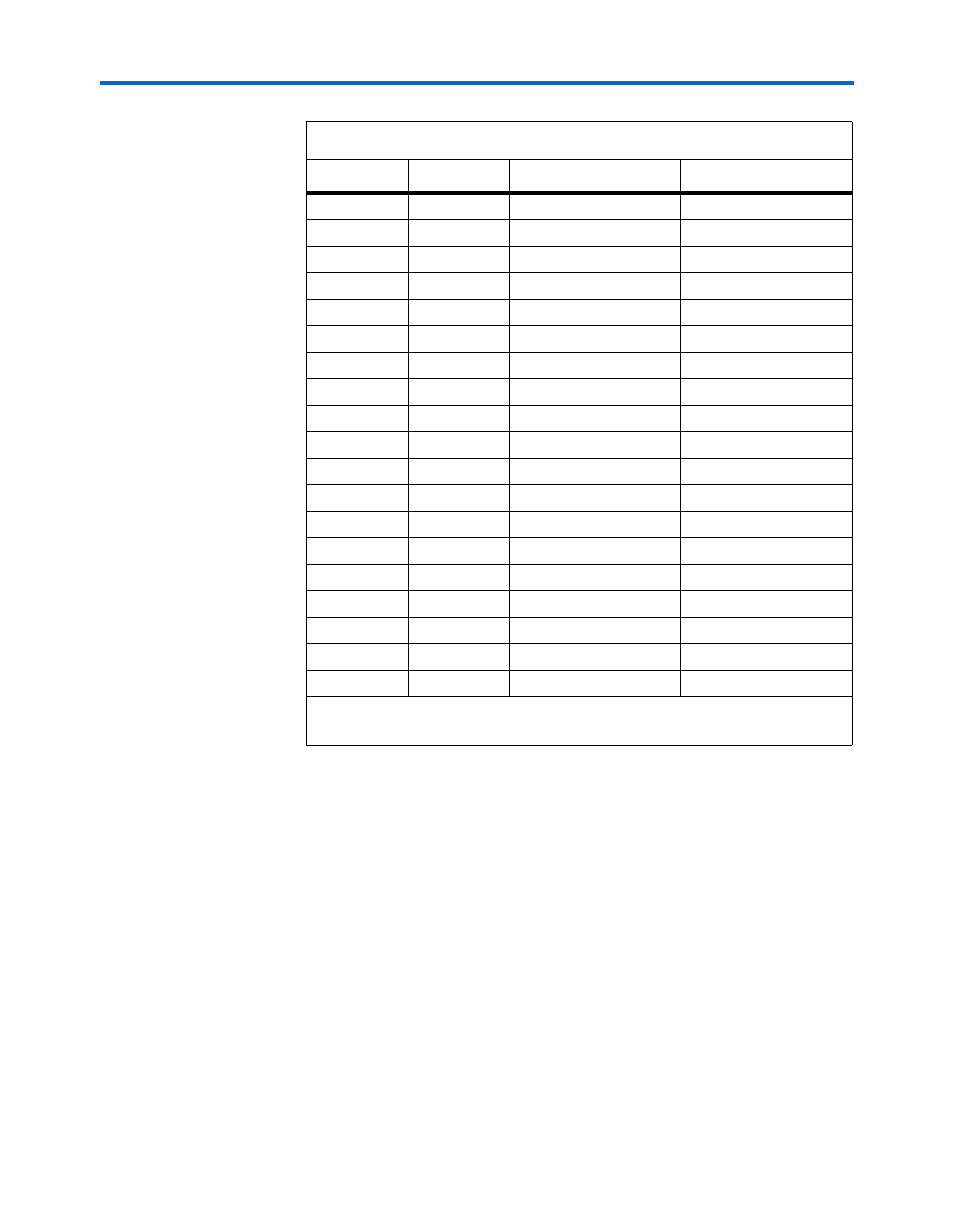

Table 2–9. Ethernet MAC/PHY Pin Table (Continued)

FPGA Pin

U4 Pin

Pin Function

Board Net Name

(1)