Set_ready(), Signal_fatal_error, Signal_sink_ready_assert – Altera Avalon Verification IP Suite User Manual

Page 135: Set_ready() -9, Signal_fatal_error -9, Signal_sink_ready_assert -9

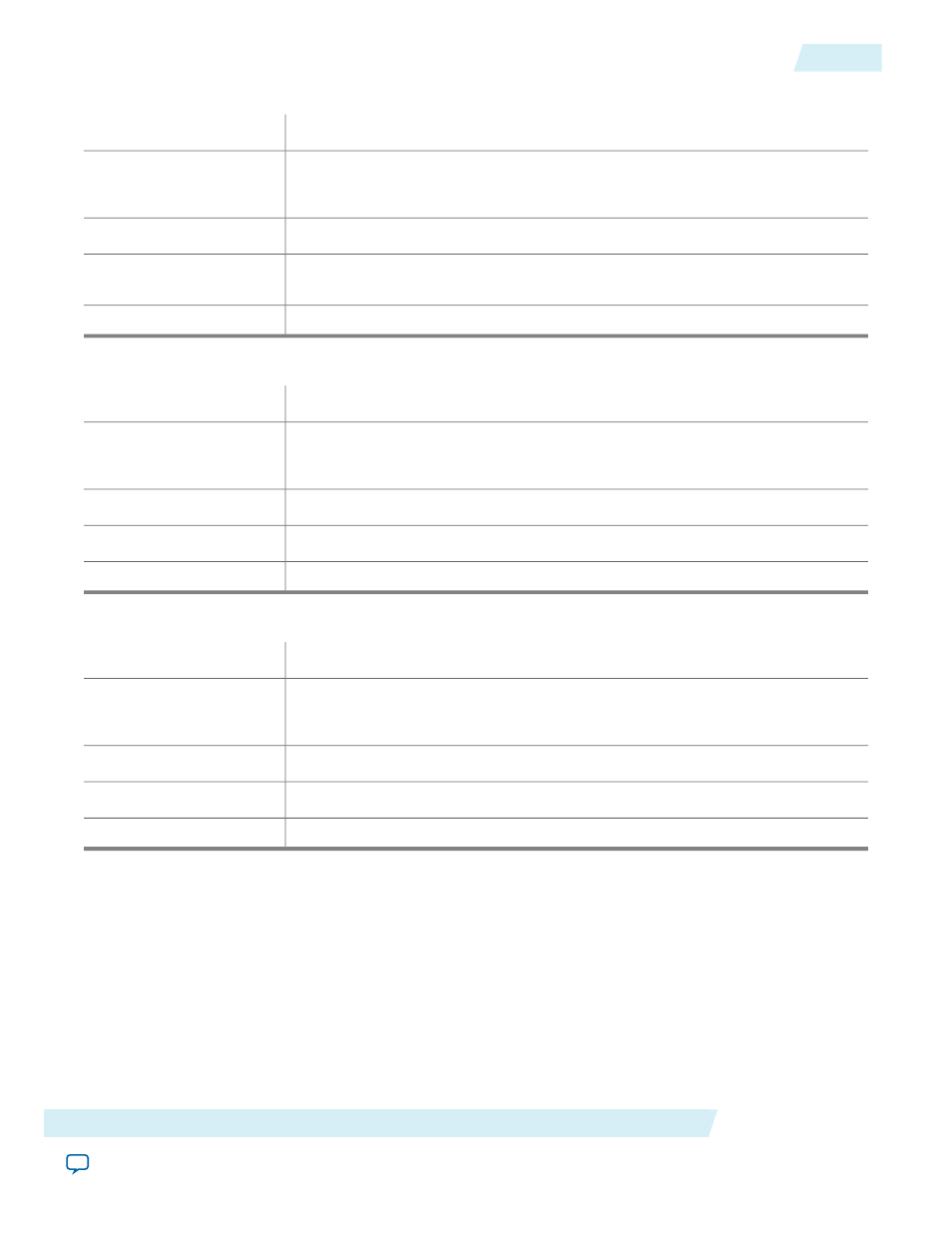

set_ready()

set_ready()

Prototype:

Verilog HDL:

read_bit

VHDL:

read_bit

,

bfm_id

,

req_if(bfm_id)

Arguments:

void

Returns:

Sets the value of the interface’s

ready

signal. To assert back pressure, deassert this

signal. The parameter

USE_READY

must be set to 1 to enable the

ready

signal.

Description:

Verilog HDL, VHDL

Language support:

signal_fatal_error

signal_fatal_error

Prototype:

Verilog HDL: None

VHDL: N.A.

Arguments:

void

Returns:

Signals that a fatal error has occurred. It terminates the simulation.

Description:

Verilog HDL

Language support:

signal_sink_ready_assert

signal_sink_ready_assert

Prototype:

Verilog HDL: None

VHDL: N.A.

Arguments:

void

Returns:

Signals that

sink_ready

is asserted, turning off back pressure.

Description:

Verilog HDL

Language support:

Altera Corporation

Avalon-ST Sink BFM

9-9

set_ready()