12 spi interface, 13 lan, 1 mdio – Artesyn SCP-P4040-4G-ENP2 Installation and Use (August 2014) User Manual

Page 45: 12 spi interface 4.13 lan, Figure 4-7, Distribution of spi bus

Functional Description

SCP-P4040-4G-ENP2 Installation and Use (6806800P60B)

45

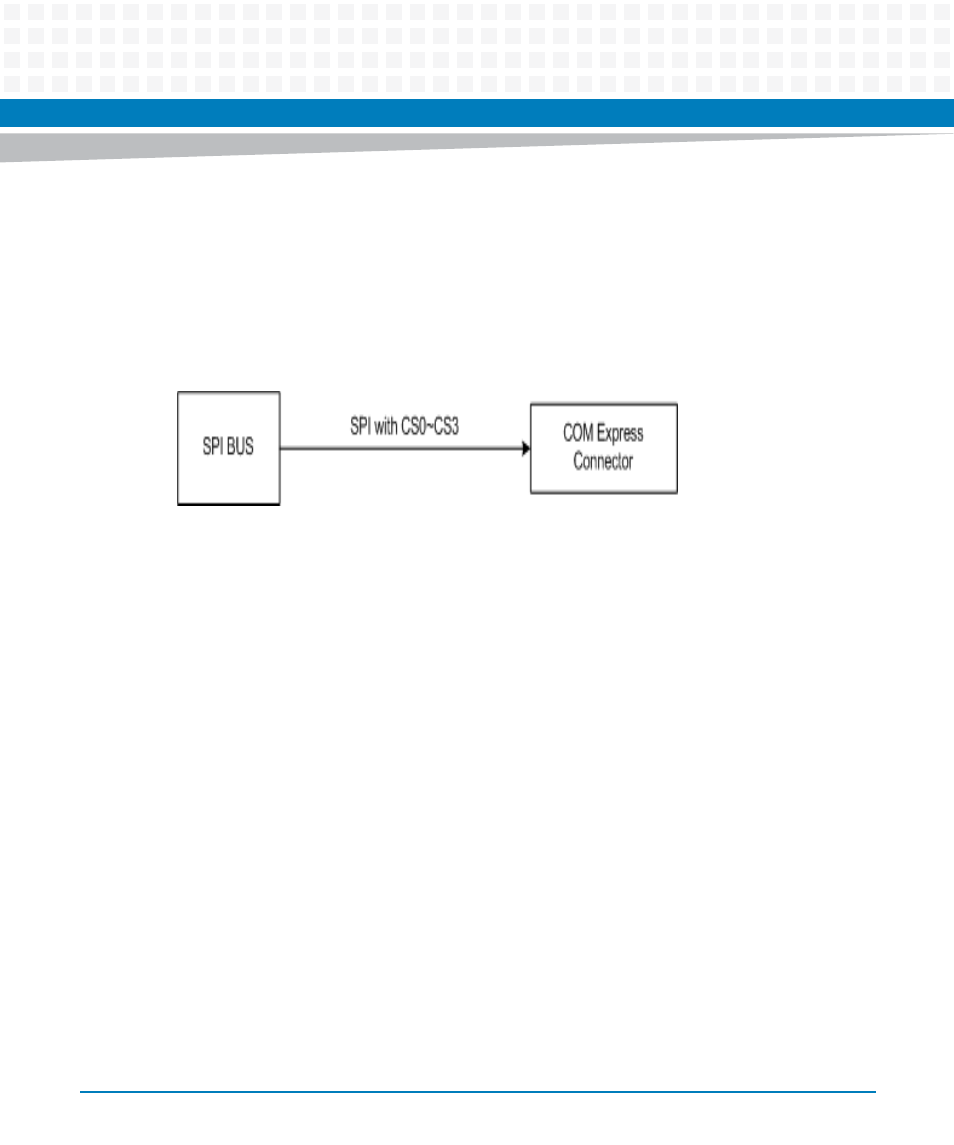

4.12 SPI Interface

SCP-P4040-4G-ENP2 provides a SPI bus with 3 chip-select signals. All SPI bus signals are routed

to COM Express connectors.

The following figure illustrates the distribution of SPI bus:

4.13 LAN

This module provides 1 GE port with LED controlling signals routing to the COM Express

connectors and the magnetic must be placed on carrier board. The interface used between

MAC and PHY BCM5482 is the RGMII bus in P4040, which is multiplexed with USB1 ULPI bus, so

RCW [EC1] should be set to 00 as RGMII protocol.

U-boot should provide the driver of dTSEC and TCP/IP protocol stack. The U-boot can use TFTP

to download images to memory.

4.13.1 MDIO

There are totally two groups of MDIO buses in P4040. The first group is called EMI1 which

complies with IEEE 802.3 Clause 22. EMI1 has two pins: EMI1_MDC and EMI1_MDIO. It is

available externally only on dTSEC0@FMan1. EMI1 is used for the communication between

dTSEC, MAC, and PHY. SGMII PHY is also managed by EMI1.

The second group is called EMI2 which complies with IEEE 802.3ae Clause 45. EMI2 has two

pins: EMI2_MDC and EMI2_MDIO. It is available externally only on 10GEC of FMan1. EMI2

is used for the communication between 10GEC and PHY.

Figure 4-7

Distribution of SPI Bus