Altera FIR Compiler User Manual

Page 66

4–24

Chapter 4: Functional Description

Timing Diagrams

© May 2011

Altera Corporation

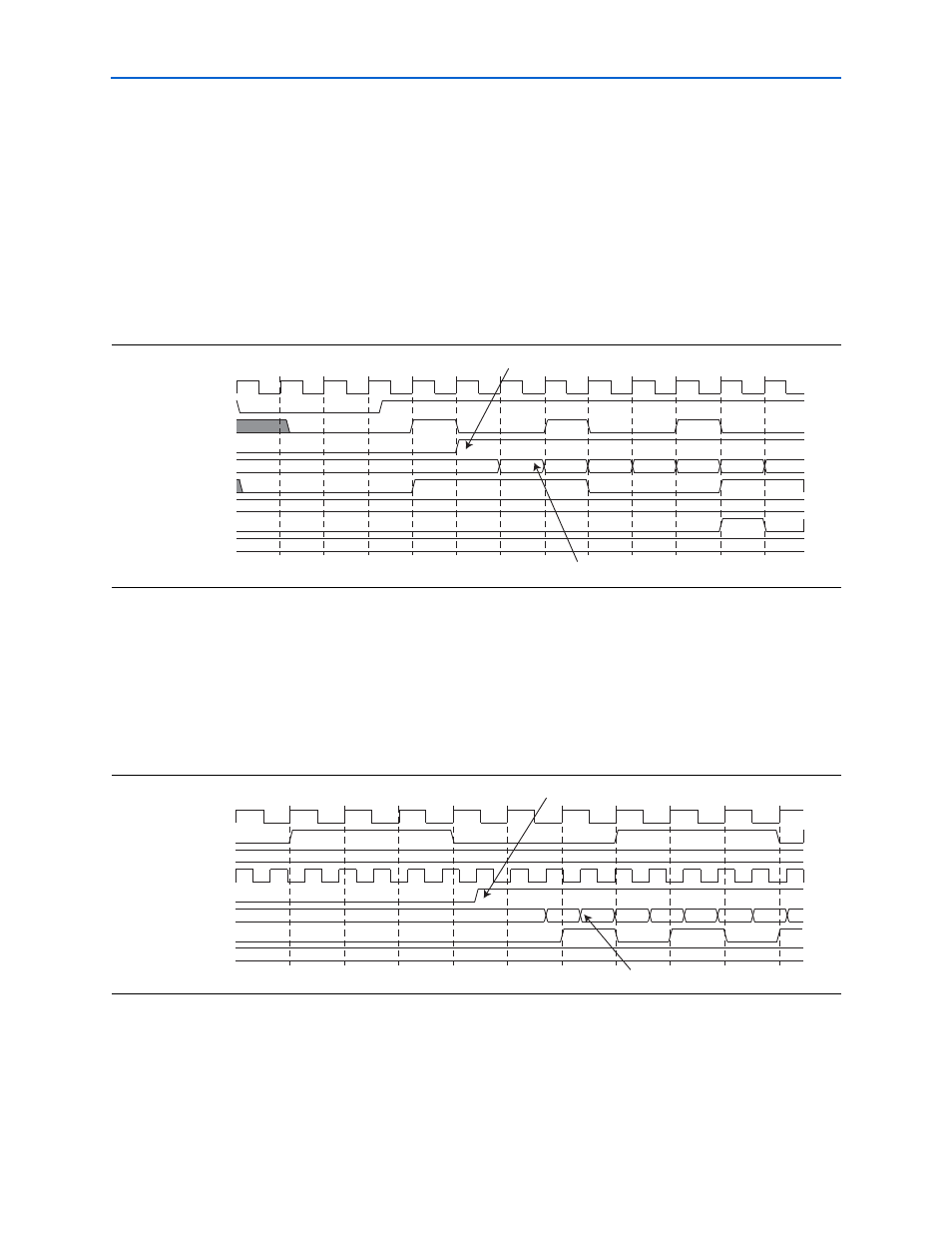

Multicycle variable reloading is faster than the fixed FIR (with reloading capability).

Coefficients need sequence adjustment using the same algorithm as fixed FIR filters

for all types of coefficient storage. The reloading clock is the same as the FIR filter

calculation clock; coef_we should be triggered by the

coef_ld

signal.

1

When the coefficients are stored in logic cells, a reloaded coefficient set reverts backs

to the original set after a reset operation.

shows the Multicycle variable coefficient reloading timing diagram when

the coefficients are stored in logic cells.

For multicycle variable FIR filters, when coefficients are stored in memory blocks,

coef_we

should be effective two clock cycles before the first

coef_in

data, and

should last until the last

coef_in data

is transmitted. Coefficients can be

transmitted from c0 to cn by a different clock.

shows the Multicycle variable coefficient reloading timing diagram when

the coefficients are stored in memory blocks.

If you use multiple coefficient sets, you can update one set of coefficients while using

another set for calculation. The signals

coef_set_in

and

coef_we

are not clocked

in and pipelined synchronously. While you update the coefficient set, you need to set

and hold the

coef_set_in

signal for several cycles before

coef_we

is asserted and

after it is de-asserted.

Figure 4–26. Multicycle Variable (Using Logic Cells) Coefficient Reloading Timing Diagram

clk

reset_n

coef_ld

coef_we

coef_in

ast_sink_ready

ast_sink_data

ast_source_valid

ast_source_data

0

-114

-12

-10

0

-16

-127

-16

0

0

Coef_we is valid one clock cycle after effective coef_ld

Input coefficients coef_in are sequence adjusted

Figure 4–27. Multicycle Variable (Using Memory Blocks) Coefficient Reloading Timing Diagram

clk

ast_sink_ready

ast_sink_data

coef_in_clk

coef_we

coef_in

ast_source_valid

ast_source_data

0

5

-114

-12

-10

0

-16

-127

-16

8

-16

0

coef_we is effective two clock cycles before first coef_in data

Coefficients from c0 to cN