Release information, Release information –4 – Altera FIR Compiler User Manual

Page 8

1–4

Chapter 1: About the FIR Compiler

Release Information

© May 2011

Altera Corporation

■

Precision control of chip resource utilization:

■

Logic cells, M512, M4K, M-RAM, MLAB, M9K, or M144K for data storage.

■

M512, M4K, M9K, M20K, MLAB or logic cells for coefficient storage.

■

Includes a resource estimator.

■

Support for run-time coefficient reloading capability and multiple coefficient sets.

■

Includes a built-in coefficient generator to enable efficient design space

exploration.

■

User-selectable output precision via rounding and saturation.

■

DSP Builder ready.

Release Information

provides information about this release of the Altera

®

FIR Compiler.

f

For more information about this release, refer to the

.

Altera verifies that the current version of the Quartus

®

II software compiles the

previous version of each MegaCore

®

function. The

report any exceptions to this verification. Altera does not verify

compilation with MegaCore function versions older than one release.

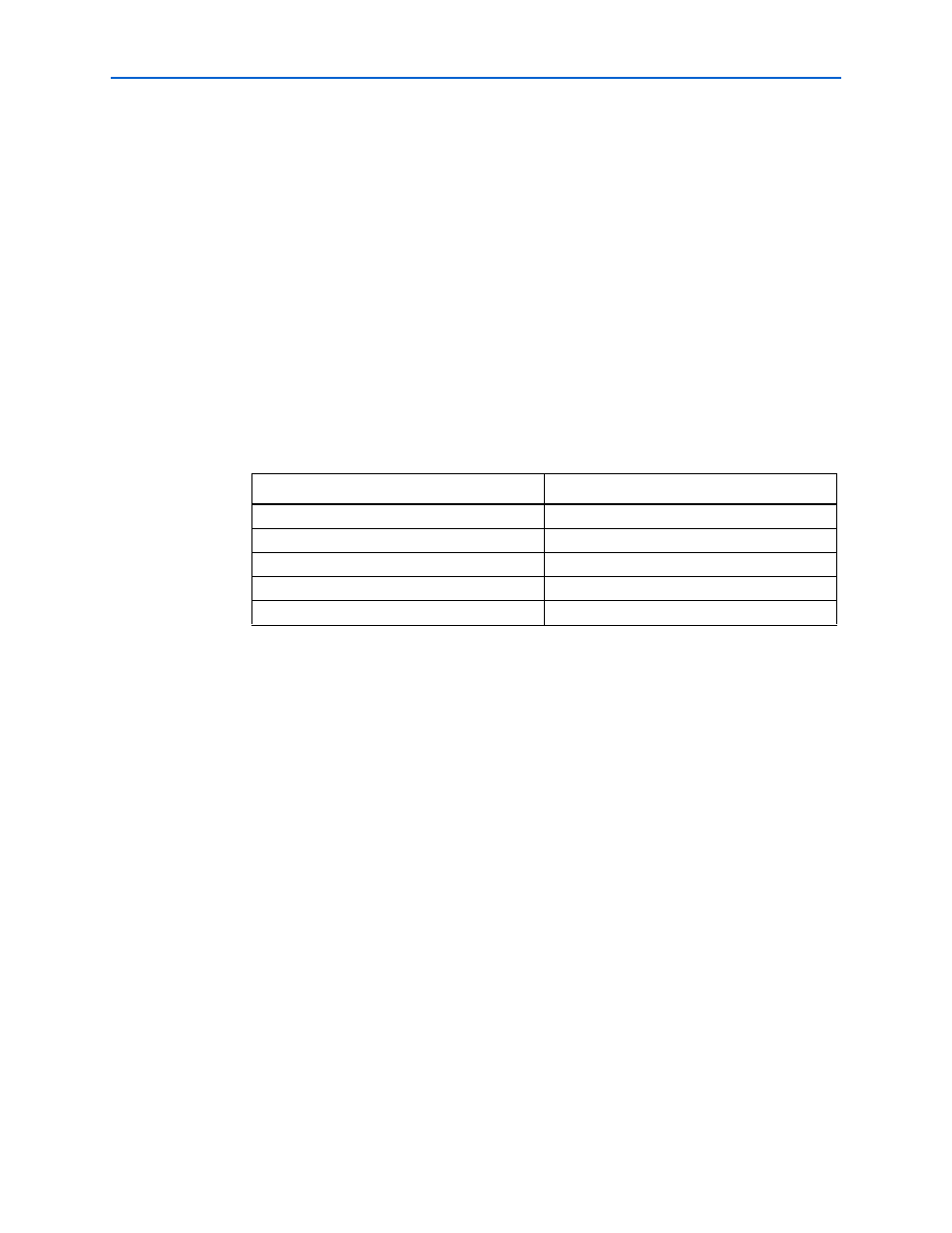

Table 1–2. FIR Compiler Release Information

Item

Description

Version

11.0

Release Date

May 2011

Ordering Code

IP-FIR

Product ID

0012

Vendor ID

6AF7