Altera I/O Buffer (ALTIOBUF) IP Core User Manual

Page 21

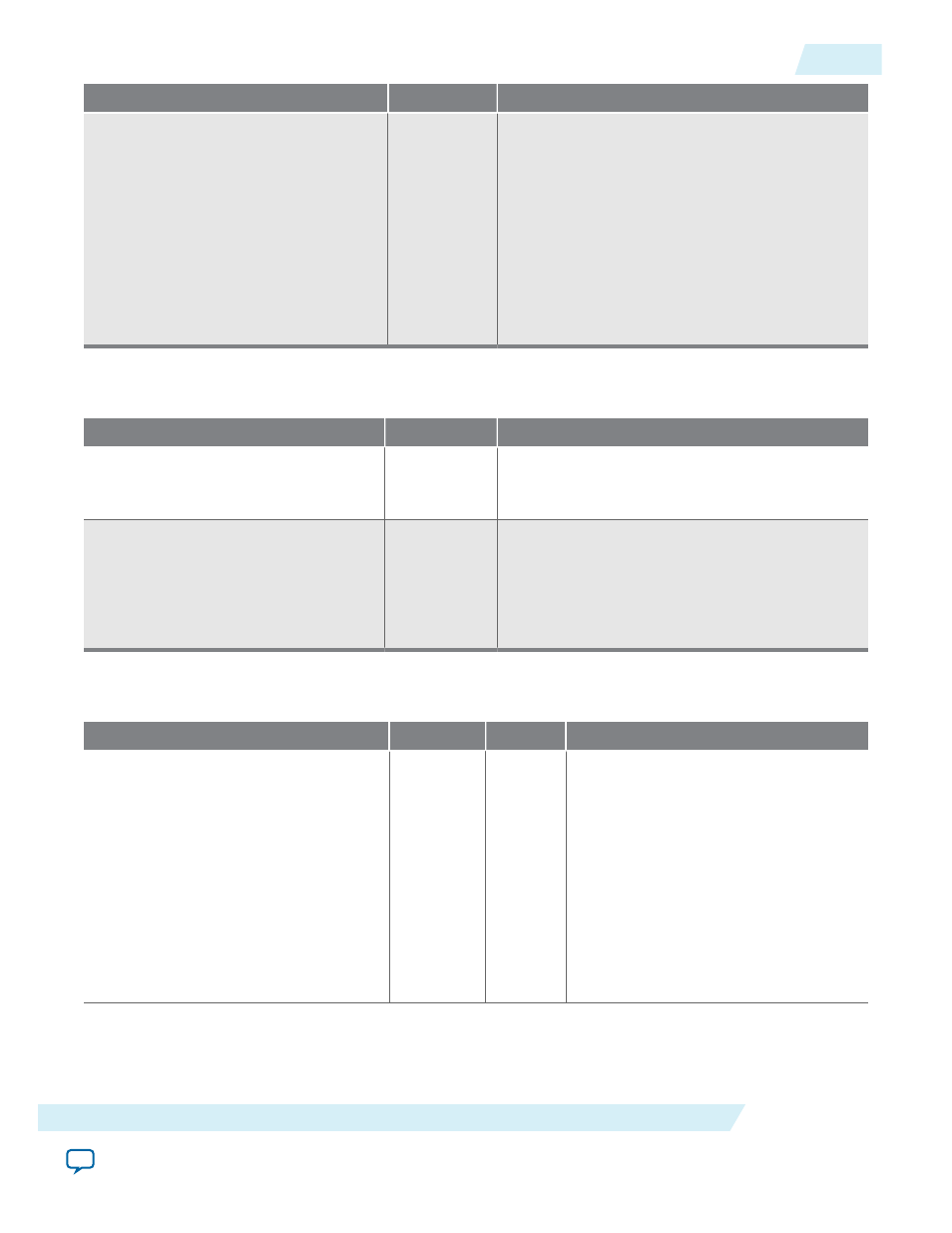

Name

Required

Description

parallelterminationcontrol_b

No

Receives the current state of the pull up and pull

down

Rt

control buses from a termination logic

block. Input port

[WIDTH_PTC * NUMBER_OF_

CHANNELS - 1..0]

wide. Port is available only

when the

USE_DIFFERENTIAL_MODE

parameter

value is TRUE. The port is available for Stratix

III device families only. Supported in Stratix

series only.

Port is available only when the

USE_DIFFEREN-

TIAL_MODE

parameter value is

TRUE.

Table 10: ALTIOBUF (As Output Buffer) Output Ports

This table lists the output ports for the ALTIOBUF IP core (as output buffer).

Name

Required

Description

dataout[]

Yes

Output buffer output port. Output port

[NUMBER_OF_CHANNELS - 1..0]

wide. The I/O

output buffer element output.

dataout_b[]

No

Differential output buffer-negative output.

Output port

[NUMBER_OF_CHANNELS - 1..0]

wide. The I/O output buffer negative output.

Port is available only when the

USE_DIFFEREN-

TIAL_MODE

parameter value is

TRUE.

Table 11: ALTIOBUF (As Output Buffer) Parameter

This table lists the parameters for the ALTIOBUF IP core (as output buffer).

Name

Required

Type

Description

ENABLE_BUS_HOLD

No

String

Specifies whether the bus hold

circuitry is enabled. Values are

TRUE

and

FALSE

. When set to

TRUE

, bus hold

circuitry is enabled, and the previous

value, instead of high impedance, is

assigned to the output port when there

is no valid input. If omitted, the default

is

FALSE

.

Currently,

ENABLE_BUS_HOLD

and

USE_

DIFFERENTIAL_MODE

cannot be used

simultaneously.

UG-01024

2014.12.15

ALTIOBUF Signals and Parameters: As Output Buffer

21

I/O Buffer (ALTIOBUF) IP Core User Guide

Altera Corporation