Altera I/O Buffer (ALTIOBUF) IP Core User Manual

Page 9

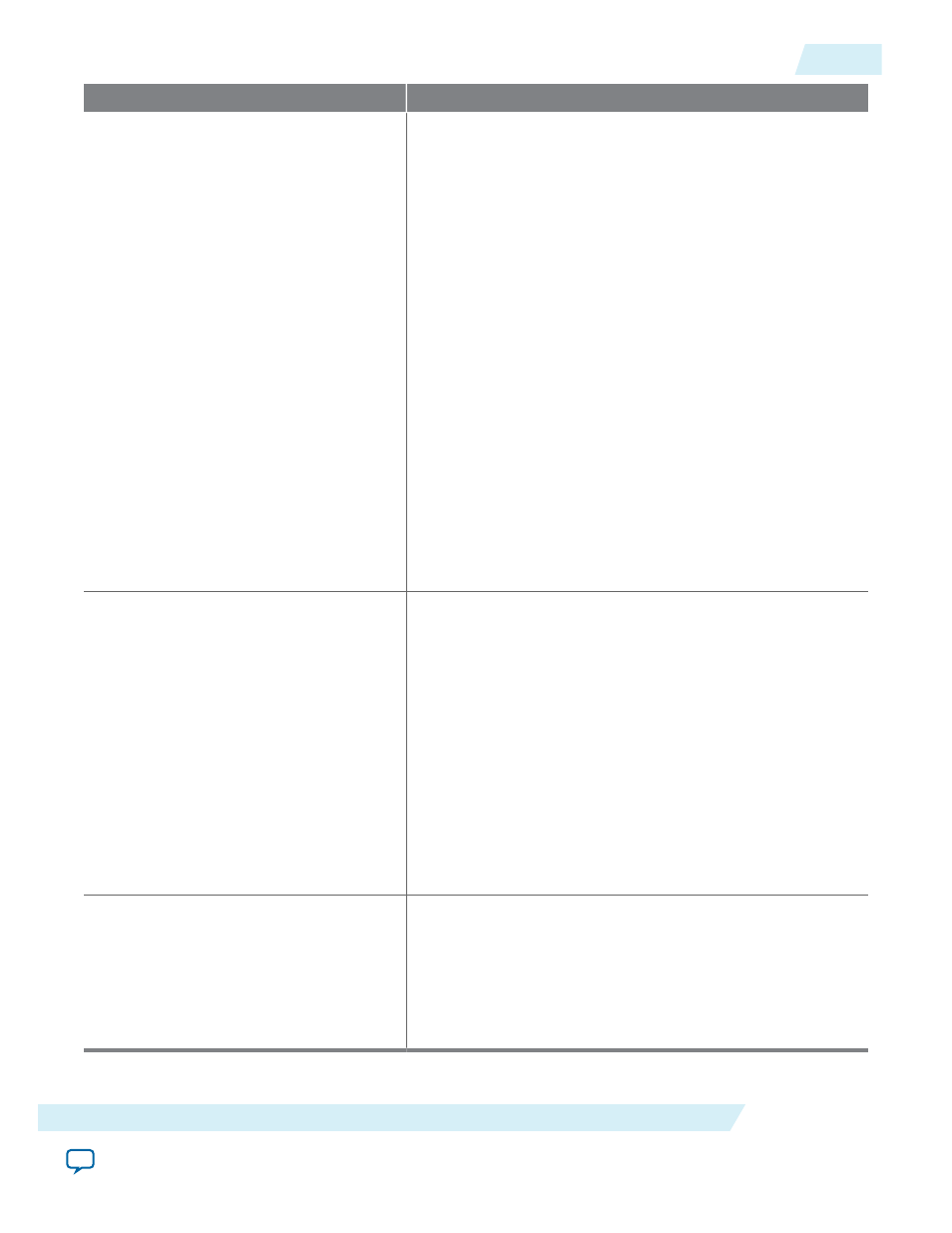

Parameter

Description

Use dynamic termination control(s)

If enabled, this port receives the command to select either

Rs

code (when input value = low) or

Rt

code (when input value =

high) from the core. Only enable

Rt

when the bi-directional I/

O is receiving input. Otherwise, it needs to be disabled so that

the output performance and power dissipation is optimal.

This option is available only for input and bidirectional

buffers.

An error is issued if parallel termination (

Rt

) is on and

dynamic termination control is not connected on a bidir pin.

An error is issued if parallel termination (

Rt

) is off and

dynamic termination control is connected on an input or

bidirectional pin.

Note that two I/Os in the same dynamic termination control

group needs to have the same dynamic termination control

signal. If the I/Os have separate dynamic termination control

signals, the Quartus II software produces a fitting error. A

dynamic termination control group is a group of pins that

share the same physical dynamic termination control signal

on the chip.

This option is not available in Cyclone III and Cyclone IV

devices.

Use series and parallel termination

controls

If enabled, this allows the series and parallel termination

control ports to be used. These ports can then be connected to

termination logic blocks to receive the Rs or Rt code from the

termination logic blocks.

This option is only available for output buffers and bidirec‐

tional buffers. The series and parallel termination control

ports are 14-bit wide for series or parallel termination.

For Cyclone III, Cyclone IV, and Cyclone V devices, this

option is available for output buffers and bidirectional buffers,

but not for input buffers. Only series termination is available.

The series termination control ports are 16-bit wide. The

width of these ports increases depending on the amount of

buffers instantiated.

Use left shift series termination control

If enabled, you can use the left shift series termination control

to get the calibrated OCT R

s

with half of the impedance value

of the external reference resistors connected to

RUP

and

RDN

pins. This option is useful in applications which required both

25-Ω and 50-Ω calibrated OCT R

s

at the same V

ccio

. For more

information, refer to I/O features chapter of the respective

device handbooks.

UG-01024

2014.12.15

ALTIOBUF Parameters

9

I/O Buffer (ALTIOBUF) IP Core User Guide

Altera Corporation