Verilog hdl prototype, Vhdl component declaration – Altera I/O Buffer (ALTIOBUF) IP Core User Manual

Page 28

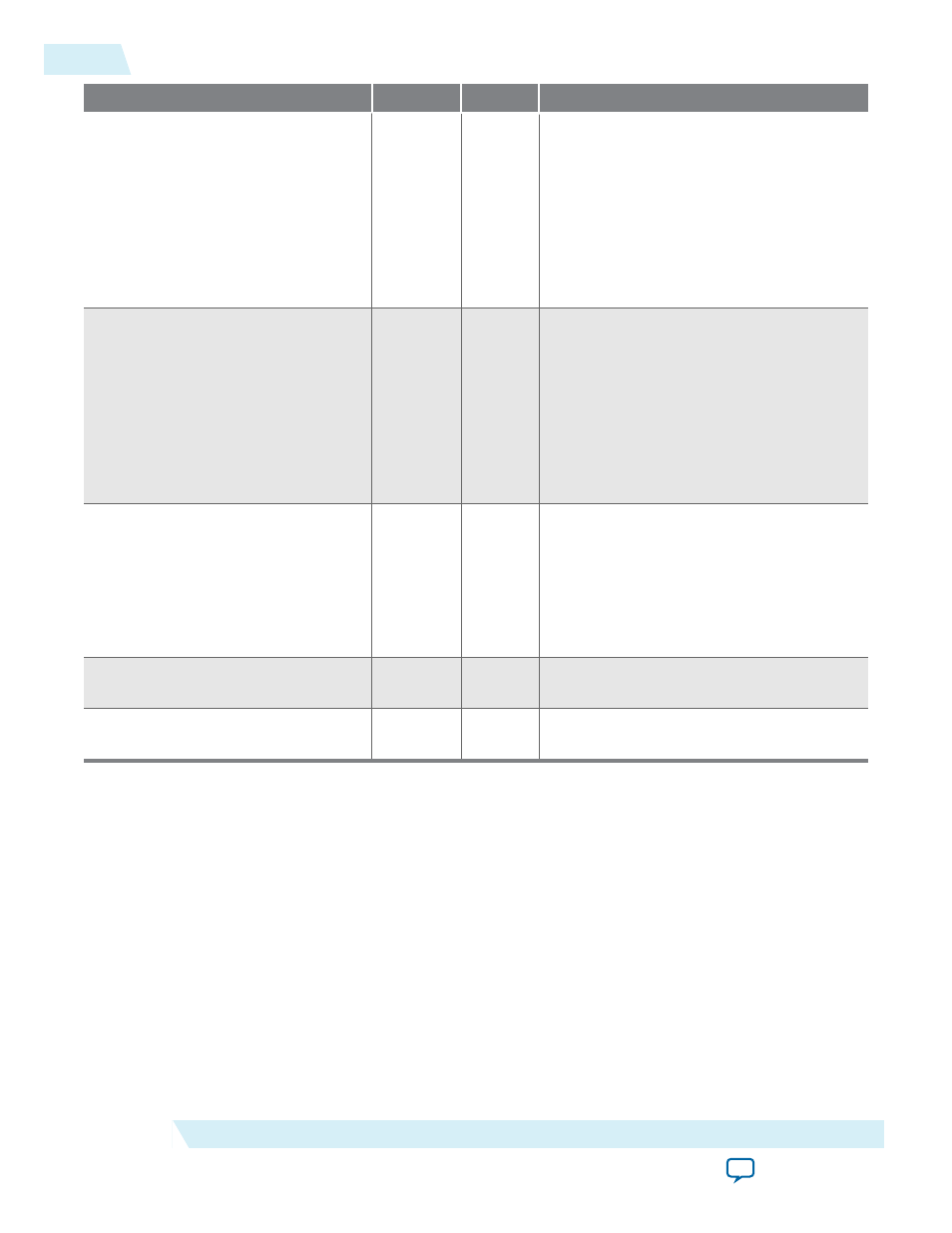

Name

Required

Type

Description

USE_OUT_DYNAMIC_DELAY_CHAIN1

No

String Specifies whether the output buffer

incorporates a user-driven dynamic delay

chain in the IP core, specifically,

IO_

CONFIG

and the first output delay cell.

Additional input ports are

io_config_

clk

,

io_config_clkena

,

io_config_

update

, and

io_config_datain

. Values

are

TRUE

and

FALSE

. If omitted, the default

is

FALSE

.

USE_OUT_DYNAMIC_DELAY_CHAIN2

No

String Specifies whether the output buffer

incorporates a user-driven dynamic delay

chain in the IP core, specifically,

IO_

CONFIG

and the second output delay cell.

Additional input ports are

io_config_

clk

,

io_config_clkena

,

io_config_

update

, and

io_config_datain

. Values

are

TRUE

and

FALSE

. If omitted, the default

is

FALSE

.

NUMBER_OF_CHANNELS

Yes

Integer Specifies the number of I/O buffers that

must be instantiated. Value must be

greater than or equal to 1. A value of 1

indicates that the buffer is a 1-bit port and

accommodates wires. A value greater than

1 indicates that the port can be connected

to a bus of width

NUMBER_OF_CHANNELS

.

WIDTH_STC

No

Integer Specifies the width setting for the series

termination control bus.

WIDTH_PTC

No

Integer Specifies the width setting for the parallel

termination control bus.

Verilog HDL Prototype

You can locate the Verilog HDL prototype in the Verilog Design File (.v) altera_mf.v in the <Quartus II

installation directory>\eda\synthesis directory.

VHDL Component Declaration

You can locate VHDL component declaration in the VHDL Design File (.vhd)

altera_mf_components.vhd in the <Quartus II installation directory>\libraries\vhdl\altera_mf

directory.

28

Verilog HDL Prototype

UG-01024

2014.12.15

Altera Corporation

I/O Buffer (ALTIOBUF) IP Core User Guide