Altera Cyclone V SoC Development Board User Manual

Page 21

Chapter 2: Board Components

2–13

FPGA Configuration

November 2013

Altera Corporation

Cyclone V SoC Development Board

Reference Manual

The MAX II CPLD EPM570GF100I5N is dedicated to the on-board USB-Blaster II

functionality only, connecting to the USB 2.0 PHY device on one side and drives JTAG

signals out the other side on the GPIO pins. This device's own dedicated JTAG

interface are routed to a small surface-mount header only intended for debugging of

first article prototypes.

A USB 2.0 Cypress EZ-USB CY7C68013A device (U51) in a 56-pin VBGA package

interfaces to a mini-USB connector.

lists the USB 2.0 PHY schematic signal names and their corresponding

MAX II CPLD pin numbers.

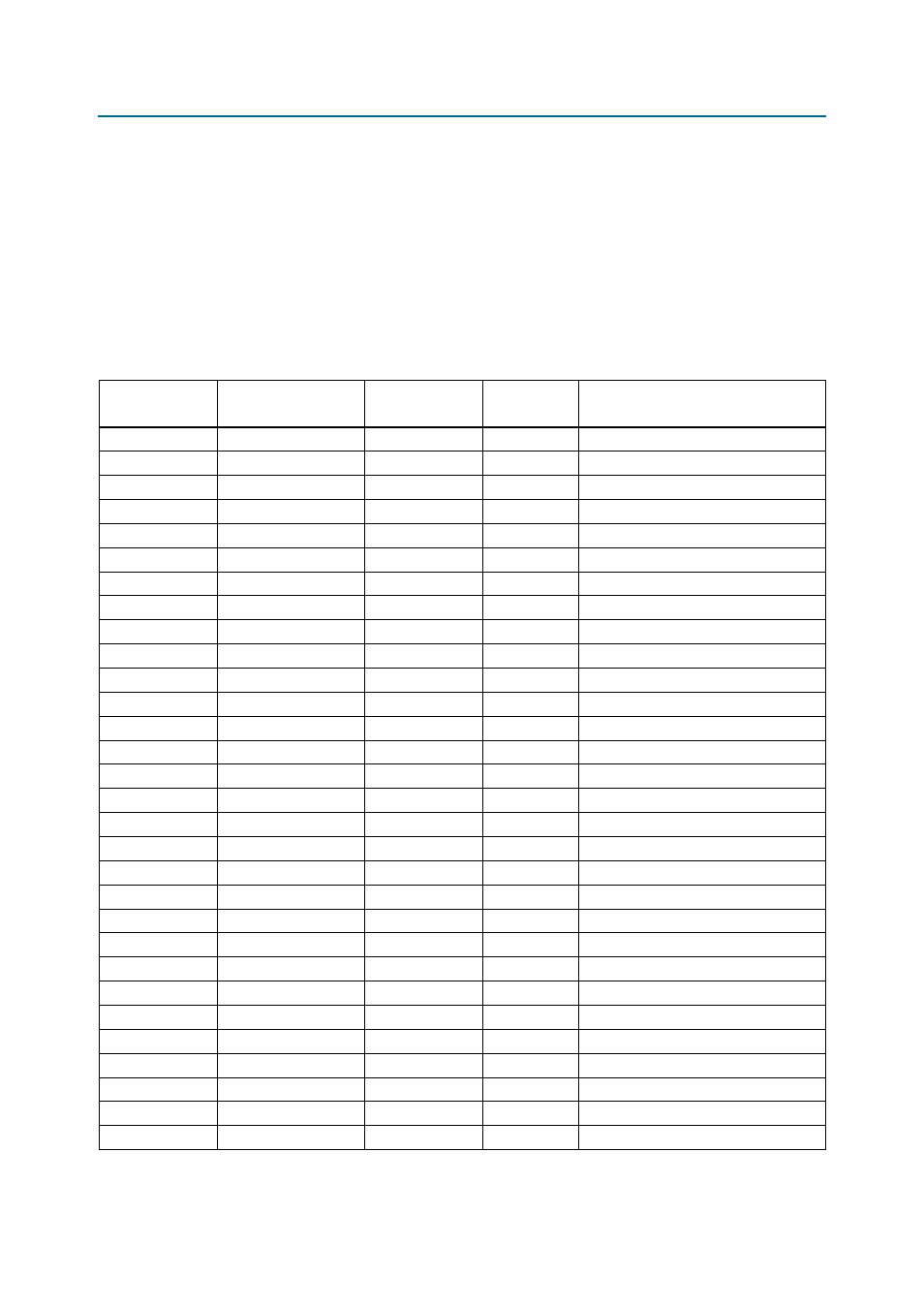

Table 2–5. USB 2.0 PHY Schematic Signal Names and Functions (Part 1 of 2)

Board Reference

(U51)

Schematic

Signal Name

MAX II CPLD Pin

Number

I/O Standard

Description

C1

24M_XTALIN

—

3.3-V

Crystal oscillator input

C2

24M_XTALOUT

—

3.3-V

Crystal oscillator output

E1

FX2_D_N

—

3.3-V

USB 2.0 PHY data

E2

FX2_D_P

—

3.3-V

USB 2.0 PHY data

H7

FX2_FLAGA

D1

3.3-V

Slave FIFO output status

G7

FX2_FLAGB

G1

3.3-V

Slave FIFO output status

H8

FX2_FLAGC

C1

3.3-V

Slave FIFO output status

G6

FX2_PA1

G3

3.3-V

USB 2.0 PHY port A interface

F8

FX2_PA2

B1

3.3-V

USB 2.0 PHY port A interface

F7

FX2_PA3

D2

3.3-V

USB 2.0 PHY port A interface

F6

FX2_PA4

D3

3.3-V

USB 2.0 PHY port A interface

C8

FX2_PA5

K4

3.3-V

USB 2.0 PHY port A interface

C7

FX2_PA6

F2

3.3-V

USB 2.0 PHY port A interface

C6

FX2_PA7

C2

3.3-V

USB 2.0 PHY port A interface

H3

FX2_PB0

G2

3.3-V

USB 2.0 PHY port B interface

F4

FX2_PB1

H8

3.3-V

USB 2.0 PHY port B interface

H4

FX2_PB2

F3

3.3-V

USB 2.0 PHY port B interface

G4

FX2_PB3

J3

3.3-V

USB 2.0 PHY port B interface

H5

FX2_PB4

F1

3.3-V

USB 2.0 PHY port B interface

G5

FX2_PB5

H1

3.3-V

USB 2.0 PHY port B interface

F5

FX2_PB6

H7

3.3-V

USB 2.0 PHY port B interface

H6

FX2_PB7

E1

3.3-V

USB 2.0 PHY port B interface

A8

FX2_PD0

H3

3.3-V

USB 2.0 PHY port D interface

A7

FX2_PD1

H2

3.3-V

USB 2.0 PHY port D interface

B6

FX2_PD2

J2

3.3-V

USB 2.0 PHY port D interface

A6

FX2_PD3

J1

3.3-V

USB 2.0 PHY port D interface

B3

FX2_PD4

J6

3.3-V

USB 2.0 PHY port D interface

A3

FX2_PD5

K3

3.3-V

USB 2.0 PHY port D interface

C3

FX2_PD6

J5

3.3-V

USB 2.0 PHY port D interface

A2

FX2_PD7

K2

3.3-V

USB 2.0 PHY port D interface