Expansion header, Character lcd, Clock circuitry – Altera Cyclone V SoC Development Board User Manual

Page 30: On-board oscillators, Expansion header –22 character lcd –22, Clock circuitry –22, On-board oscillators –22

2–22

Chapter 2: Board Components

Clock Circuitry

Cyclone V SoC Development Board

November 2013

Altera Corporation

Reference Manual

Expansion Header

The development board includes an expansion header (J23) to connect a daughter

card from Linear Technology. The interface connects to the SPI master or I

2

C ports of

the HPS to allow bidirectional communication with two types of protocols. The 14-pin

header also allows GPIO, SPI, and I

2

C extension for user purposes if there are no

interface card available.

The LTC_EXP_SPI_I2C jumper (J31) sets the interfaces type. When J31 is shunted, SPI

interface is used. When J31 is not shunted, I

2

C interface is used.

Character LCD

The development board includes a single 10-pin 0.1" pitch single-row header that

interfaces to a 2 line × 16 character Lumex character LCD using standard I

2

C interface

connected to the HPS. The character LCD has a two headers that mount directly to the

board's 10-pin header, so it can be easily removed for access to components under the

display. You can also use the header for debugging, I

2

C expansion, or other purposes.

f

For more information such as timing, character maps, interface guidelines, and other

related documentation, visi

Clock Circuitry

This section describes the board's clock inputs and outputs.

On-Board Oscillators

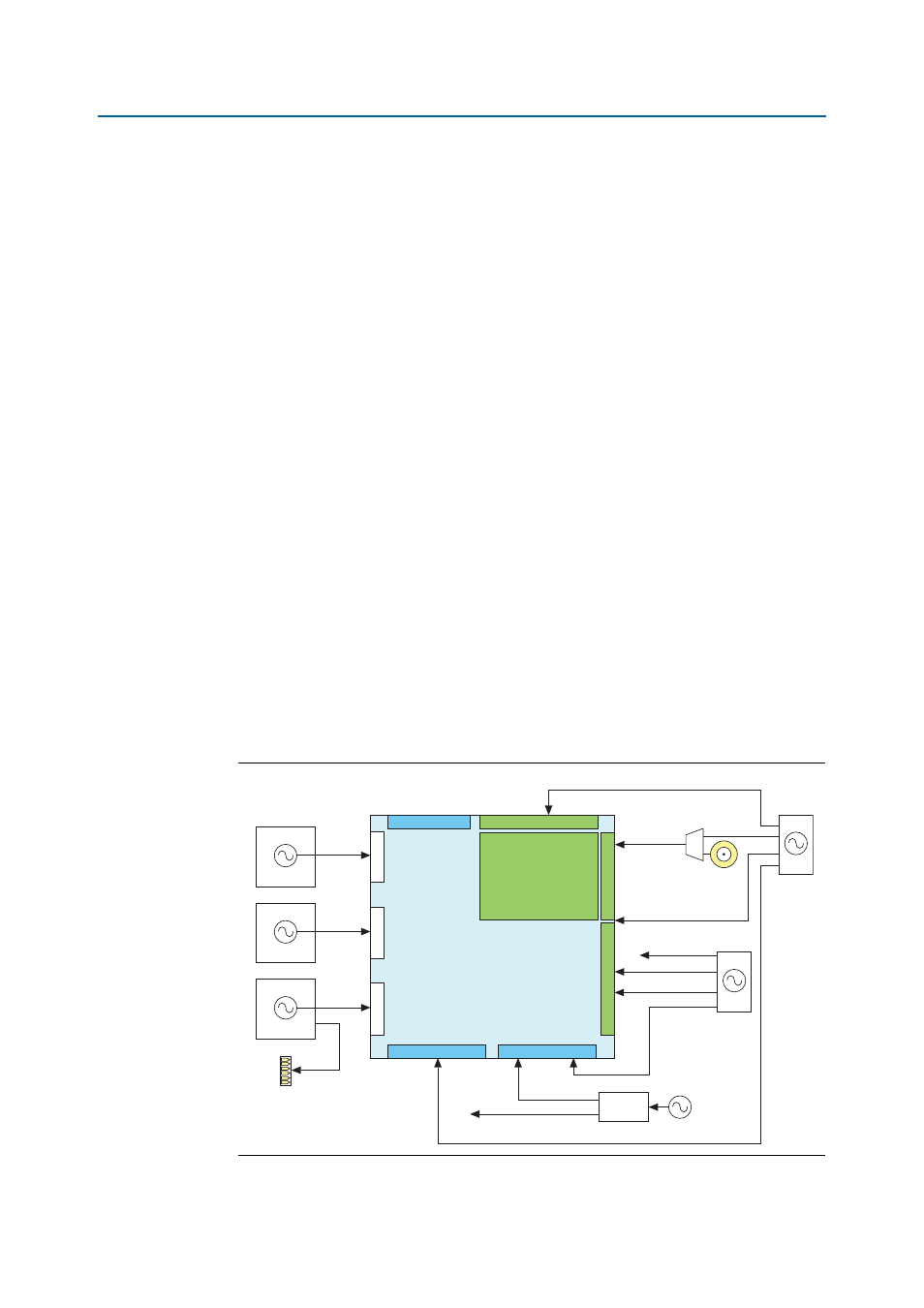

Figure 2–5

shows the default frequencies of all external clocks going to the

Cyclone V SoC development board.

Figure 2–5. Cyclone V SoC Development Board Clocks

Cyclone V SX C6

Bank 8

HPS Peripherals

HPS Core

HPS Memor

y Interf

ace

Bank 5

Bank 3

Bank 4

Bank 0L

Bank 1L

Bank 2L

REFCLK2

Si570

100 MHz/I

2

C

REFCLK1

Si571

148.5 MHz/I

2

C

REFCLK0

Si52112

100 MHz

PCIe

Socket

Si5338

CLK_OSC1

25 MHz

CLK5p

156.25 MHz

MAXV, 100 MHz

CLK5n, 100 MHz

Dual_ENET_PHY

CLK5n 25 MHz

CLK2p

25 MHz

CLK0p

100 MHz

SL18860C

MAXV

50 MHz

Si5335

50 MHz

CLK_OSC2

25 MHz

ICS830521

SMA

CLK3p

50 MHz