10/100/1000 ethernet (hps), 10/100/1000 ethernet (hps) –26 – Altera Cyclone V SoC Development Board User Manual

Page 34

2–26

Chapter 2: Board Components

Components and Interfaces

Cyclone V SoC Development Board

November 2013

Altera Corporation

Reference Manual

10/100/1000 Ethernet (HPS)

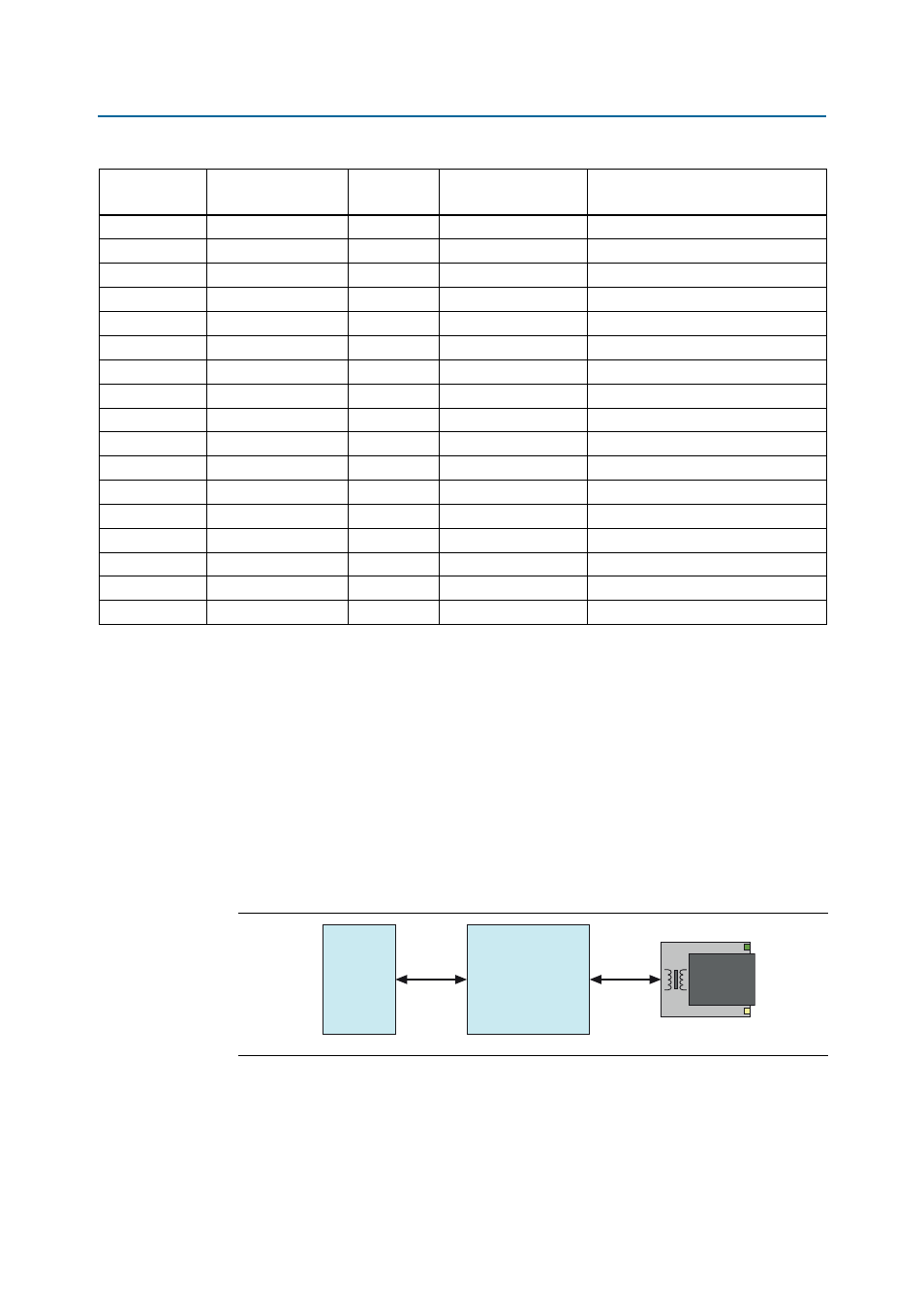

The development board supports an RJ-45 10/100/1000 base-T Ethernet using an

external Micrel KSZ9021RN PHY and the HPS EMAC. The PHY-to-MAC interface

employs RGMII connection using four data lines at 250 Mbps each for a connection

speed of 1 Gbps.

The Micrel KSZ9021RN PHY uses 2.5-V or 3.3-V power rails. The PHY interfaces to an

RJ-45 model with internal magnetics that can be used for driving copper lines with

Ethernet traffic.

shows the RGMII interface between the FPGA (MAC) and Micrel

KSZ9021RN PHY.

B11

PCIE_WAKEN

LVTTL

W21

Wake signal

A17

PCIE_RX_N0

1.5-V PCML

AE1

Receive bus

A22

PCIE_RX_N1

1.5-V PCML

AC1

Receive bus

A26

PCIE_RX_N2

1.5-V PCML

AA1

Receive bus

A30

PCIE_RX_N3

1.5-V PCML

W1

Receive bus

A16

PCIE_RX_P0

1.5-V PCML

AE2

Receive bus

A21

PCIE_RX_P1

1.5-V PCML

AC2

Receive bus

A25

PCIE_RX_P2

1.5-V PCML

AA2

Receive bus

A29

PCIE_RX_P3

1.5-V PCML

W2

Receive bus

B15

PCIE_TX_N0

1.5-V PCML

AD3

Transmit bus

B20

PCIE_TX_N1

1.5-V PCML

AB3

Transmit bus

B24

PCIE_TX_N2

1.5-V PCML

Y3

Transmit bus

B28

PCIE_TX_N3

1.5-V PCML

V3

Transmit bus

B14

PCIE_TX_P0

1.5-V PCML

AD4

Transmit bus

B19

PCIE_TX_P1

1.5-V PCML

AB4

Transmit bus

B23

PCIE_TX_P2

1.5-V PCML

Y4

Transmit bus

B27

PCIE_TX_P3

1.5-V PCML

V4

Transmit bus

Table 2–18. PCI Express Pin Assignments, Schematic Signal Names, and Functions (Part 2 of 2)

Board

Reference (J18)

Schematic Signal

Name

I/O Standard

Cyclone V SoC Device

Pin Number

Description

Figure 2–7. RGMII Interface between FPGA (MAC) and PHY

RGMII

MAC

Single-Port RGMII

Micrel KSZ9021RN

RJ-45