Rs-232 uart (hps), Can bus (hps), Rs-232 uart (hps) –34 can bus (hps) –34 – Altera Cyclone V SoC Development Board User Manual

Page 42

2–34

Chapter 2: Board Components

Components and Interfaces

Cyclone V SoC Development Board

November 2013

Altera Corporation

Reference Manual

RS-232 UART (HPS)

The development board supports a UART interface that connects to a mini-USB

connector (J8) using a FT232RQ-REEL USB-to-UART bridge. The maximum

supported rate for this interface is 1 Mbps. Board reference D14 and D15 are the

UART LEDs that illuminate to indicate TX and RX activity.

lists the RS-232 UART pin assignments, signal names, and functions. The

signal names and types are relative to the Cyclone V SoC in terms of I/O setting and

direction.

CAN Bus (HPS)

The development board supports one controller area network (CAN) bus through a

DB-9 male connector. The CAN bus is multi-master broadcast serial bus standard for

connecting electronic control units (ECUs). The maximum supported rate for this

interface is 1 Mbps. This interface uses a dedicated CAN controller inside the HPS. A

PHY device (U50) is connected in between the HPS and the DB-9 male connector.

143

HSMA_TX_D_P15

B13

LVDS or 2.5-V LVDS TX bit 15 or CMOS bit 68

144

HSMA_RX_D_P15

C13

LVDS or 2.5-V LVDS RX bit 15 or CMOS bit 69

145

HSMA_TX_D_N15

A13

LVDS or 2.5-V LVDS TX bit 15n or CMOS bit 70

146

HSMA_RX_D_N15

B12

LVDS or 2.5-V LVDS RX bit 15n or CMOS bit 71

149

HSMA_TX_D_P16

C12

LVDS or 2.5-V LVDS TX bit 16 or CMOS bit 72

150

HSMA_RX_D_P16

F15

LVDS or 2.5-V LVDS RX bit 16 or CMOS bit 73

151

HSMA_TX_D_N16

B11

LVDS or 2.5-V LVDS TX bit 16n or CMOS bit 74

152

HSMA_RX_D_N16

F14

LVDS or 2.5-V LVDS RX bit 16n or CMOS bit 75

155

HSMA_CLK_OUT_P2

E7

LVDS or 2.5-V LVDS or CMOS clock out 2 or CMOS bit 76

156

HSMA_CLK_IN_P2

H15

LVDS or 2.5-V LVDS or CMOS clock in 2 or CMOS bit 77

157

HSMA_CLK_OUT_N2

E6

LVDS or 2.5-V LVDS or CMOS clock out 2 or CMOS bit 78

158

HSMA_CLK_IN_N2

G15

LVDS or 2.5-V LVDS or CMOS clock in 2 or CMOS bit 79

160

HSMA_PRSNTN

AD12

2.5-V CMOS

HSMC port A presence detect

Table 2–23. HSMC Interface Pin Assignments, Schematic Signal Names, and Functions (Part 4 of 4)

Board

Reference (J12)

Schematic Signal

Name

Cyclone V SoC

Pin Number

I/O Standard

Description

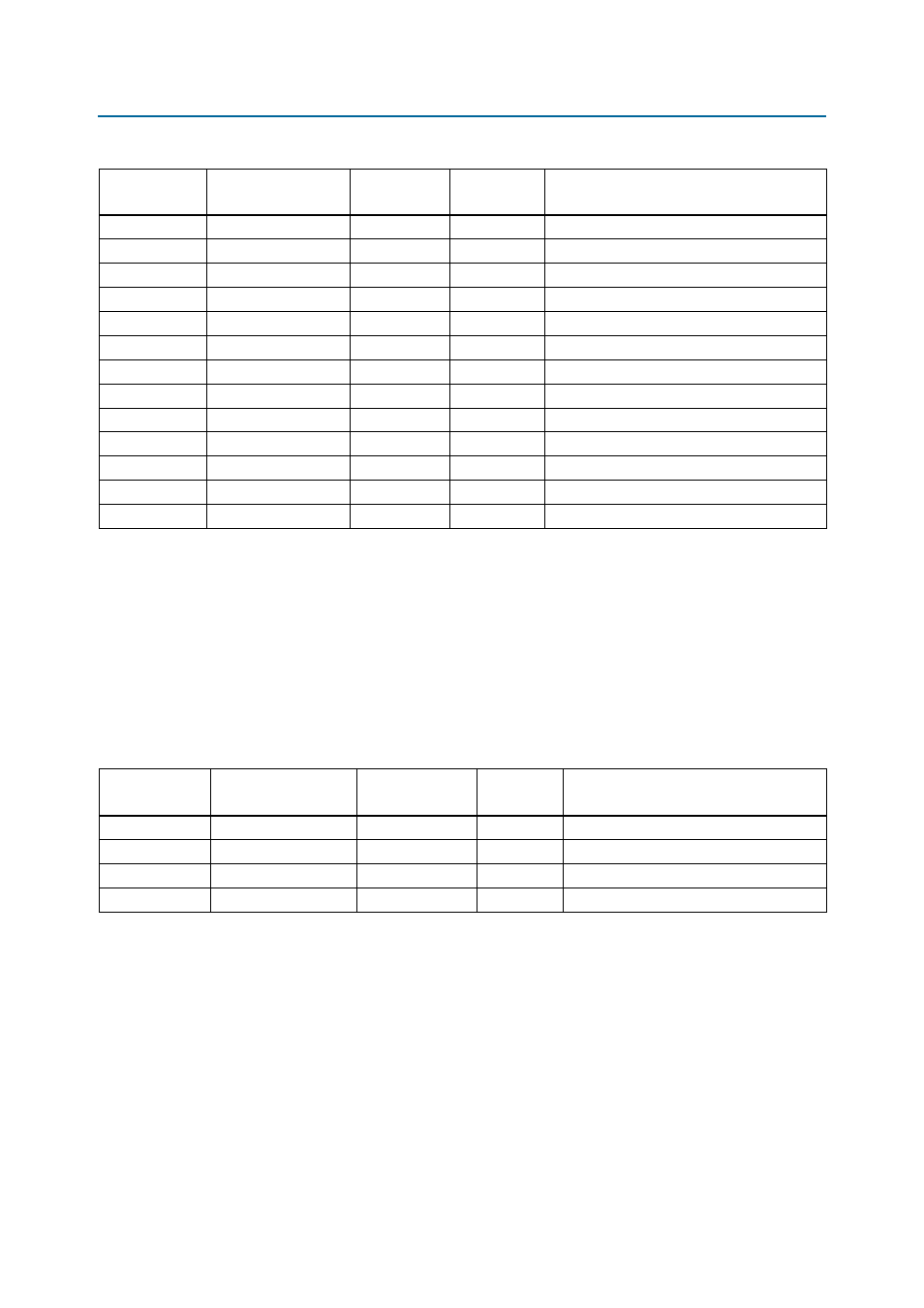

Table 2–24. RS-232 UART Schematic Signal Names and Functions

Board

Reference (U17)

Schematic

Signal Name

Cyclone V SoC

Pin Number

I/O Standard

Description

2

UART_TX

D24

3.3-V

Transmit data

30

UART_RX

E24

3.3-V

Receive data

18

RESET_HPS_UART_N

—

3.3-V

Reset

11

POWER_EN

—

3.3-V

Power