Altera Cyclone V SoC Development Board User Manual

Page 37

Chapter 2: Board Components

2–29

Components and Interfaces

November 2013

Altera Corporation

Cyclone V SoC Development Board

Reference Manual

The PHY uses a multi-level POR bootstrap encoding scheme to allow a small set of

I/O pins to set up a very large number of default settings within the device. The

related I/O pins have integrated pull-up or pull-down resistors to configure the

device. To change the configuration, connect an external resistor of maximum 5 k

Ω to

lists the level encoding scheme.

46

ENET1_TX_D3

AB26

2.5-V

MII transmit data bus

48

ENET1_TX_EN

AB22

2.5-V

MII transmit enable

65

ENET2_ACT_LED

—

2.5-V

Receive data active LED

67

ENET2_LINK_LED

—

2.5-V

Transmit data active LED

4

ENET2_MDI_RX_N

—

2.5-V

Media dependent interface

5

ENET2_MDI_RX_P

—

2.5-V

Media dependent interface

6

ENET2_MDI_TX_N

—

2.5-V

Media dependent interface

7

ENET2_MDI_TX_P

—

2.5-V

Media dependent interface

41

ENET2_RX_CLK

AH30

2.5-V

MII receive clock

35

ENET2_RX_D0

AF29

2.5-V

MII receive data bus

36

ENET2_RX_D1

AF30

2.5-V

MII receive data bus

37

ENET2_RX_D2

AD26

2.5-V

MII receive data bus

38

ENET2_RX_D3

AC27

2.5-V

MII receive data bus

39

ENET2_RX_DV

AC28

2.5-V

MII receive data valid

40

ENET2_RX_ERROR

V25

2.5-V

MII receive error

29

ENET2_TX_CLK_FB

AG30

2.5-V

25-MHz MII transmit clock

23

ENET2_TX_D0

AG27

2.5-V

MII transmit data bus

24

ENET2_TX_D1

AG28

2.5-V

MII transmit data bus

25

ENET2_TX_D2

AF28

2.5-V

MII transmit data bus

26

ENET2_TX_D3

V23

2.5-V

MII transmit data bus

28

ENET2_TX_EN

W24

2.5-V

MII transmit enable

1

ENET_DUAL_RESETN

AJ1

2.5-V

Device reset

62

ENET_FPGA_MDC

H12

2.5-V

Management bus data clock

63

ENET_FPGA_MDIO

H13

2.5-V

Management bus data

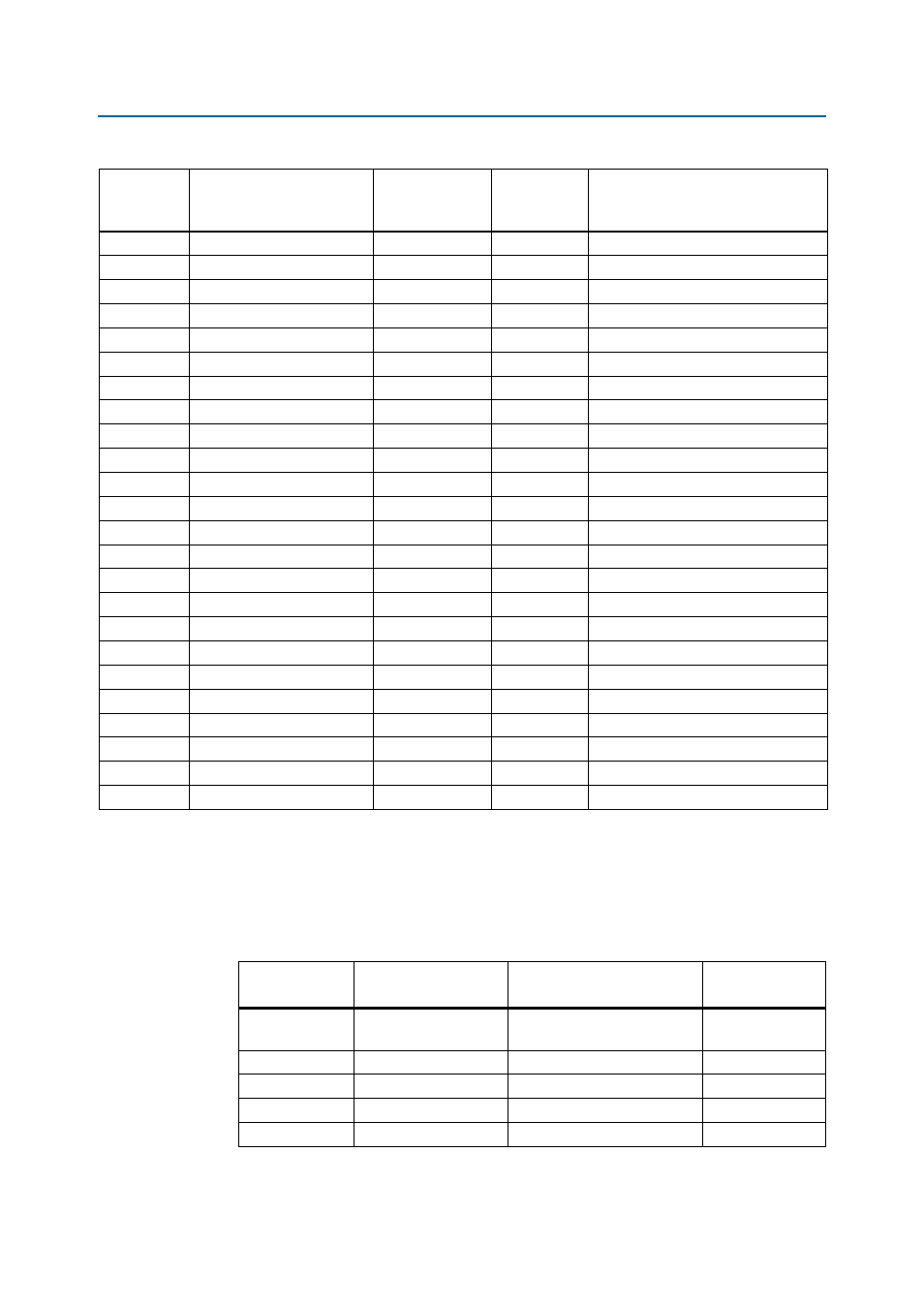

Table 2–21. Ethernet PHY Pin Assignments, Signal Names and Functions (Part 2 of 2)

Board

Reference

(U45)

Schematic Signal Name

Cyclone V SoC

Pin Number

I/O Standard

Description

Table 2–22. Ethernet PHY (FPGA) Bootstrap Encoding Scheme

Board Reference

(U11)

Schematic Signal Name

Description

Strapping Option

36

ENET2_RX_D1

Auto-negotiation disabled.

100 base-T default.

Pulled low

35

ENET2_RX_D0

Full duplex operation

Pulled high

41

ENET2_RX_CLK

Disable quick auto negotiation

Pulled low

58

ENET1_RX_ERROR

MII mode operation

Pulled low

59

ENET1_RX_CLK

AUTOMDI-X enabled

Pulled high