10/100 ethernet (fpga), 10/100 ethernet (fpga) –28 – Altera Cyclone V SoC Development Board User Manual

Page 36

2–28

Chapter 2: Board Components

Components and Interfaces

Cyclone V SoC Development Board

November 2013

Altera Corporation

Reference Manual

10/100 Ethernet (FPGA)

The development board supports an RJ-45 10/100 base-T Ethernet using an external

Renesas uPD60620A PHY. This PHY supports EtherCAT, Ethernet IRT and DLR

features using 3rd party MAC IP. The PHY-to-MAC interface employs MII connection

using four data lines at 25 Mbps each for a connection speed of 100 Mbps.

The PHY uses 3.3-V power rails and requires a 25 MHz reference clock to be driven

from a dedicated oscillator. The PHY interfaces to a dual RJ-45 model with internal

magnetics that can be used for driving copper lines with Ethernet traffic.

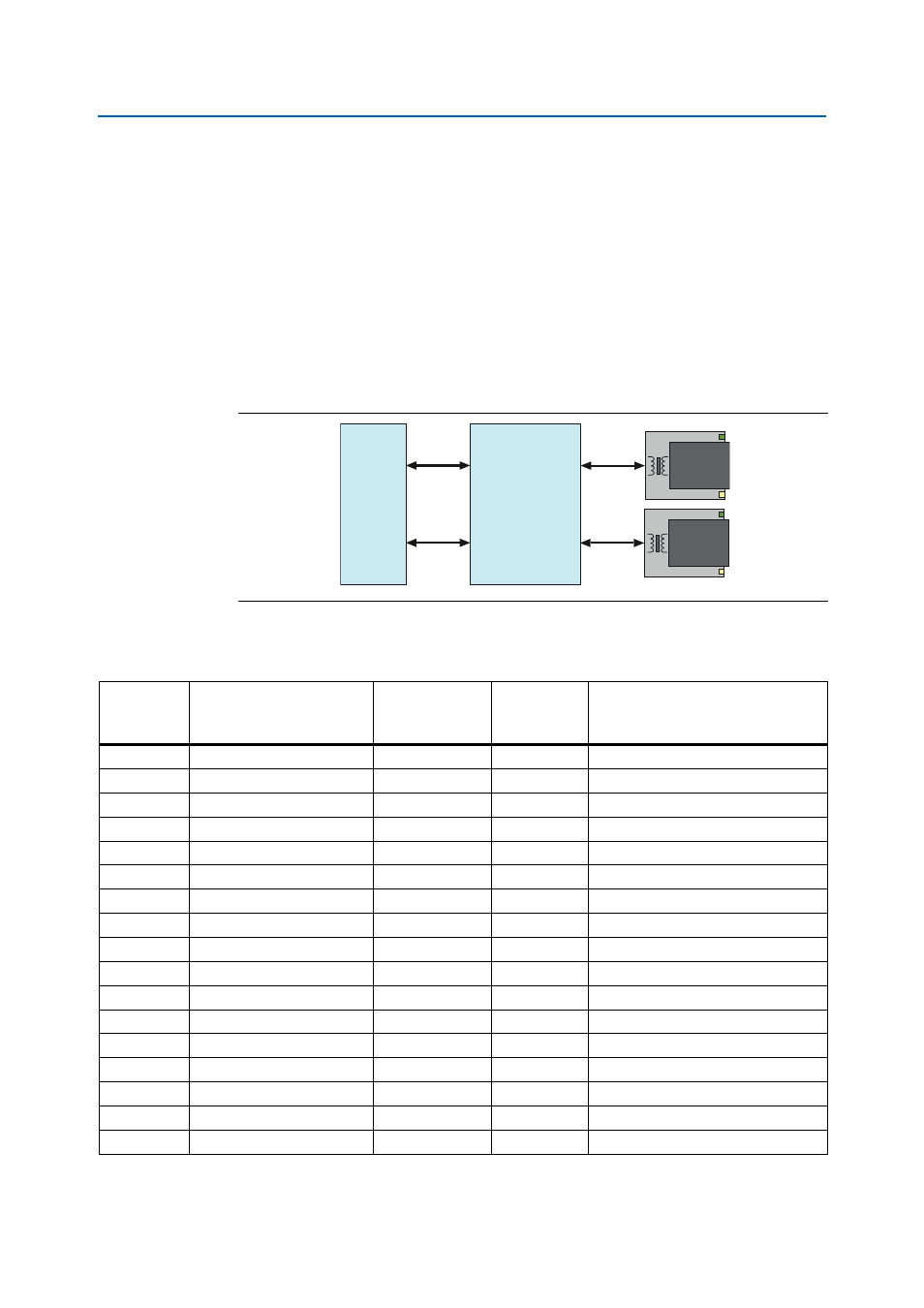

shows the MII interface between the FPGA (MAC) and Renesas

uPD60620A PHY.

lists the Ethernet PHY interface pin assignments.

Figure 2–8. MII Interface between FPGA (MAC) and PHY

FPGA MII

MAC

Dual-Port RGMII

Renesas

uPD60620A

RJ-45

RJ-45

Table 2–21. Ethernet PHY Pin Assignments, Signal Names and Functions (Part 1 of 2)

Board

Reference

(U45)

Schematic Signal Name

Cyclone V SoC

Pin Number

I/O Standard

Description

68

ENET1_ACT_LED

—

2.5-V

Receive data active LED

69

ENET1_LINK_LED

—

2.5-V

Transmit data active LED

18

ENET1_MDI_RX_N

—

2.5-V

Media dependent interface

17

ENET1_MDI_RX_P

—

2.5-V

Media dependent interface

16

ENET1_MDI_TX_N

—

2.5-V

Media dependent interface

15

ENET1_MDI_TX_P

—

2.5-V

Media dependent interface

59

ENET1_RX_CLK

Y24

2.5-V

MII receive clock

53

ENET1_RX_D0

AB23

2.5-V

MII receive data bus

54

ENET1_RX_D1

AA24

2.5-V

MII receive data bus

55

ENET1_RX_D2

AB25

2.5-V

MII receive data bus

56

ENET1_RX_D3

AE27

2.5-V

MII receive data bus

57

ENET1_RX_DV

Y23

2.5-V

MII receive data valid

58

ENET1_RX_ERROR

AE28

2.5-V

MII receive error

49

ENET1_TX_CLK_FB

W25

2.5-V

25-MHz MII transmit clock

43

ENET1_TX_D0

W20

2.5-V

MII transmit data bus

44

ENET1_TX_D1

Y21

2.5-V

MII transmit data bus

45

ENET1_TX_D2

AA25

2.5-V

MII transmit data bus