Ethernet mac/phy, Expansion prototype connector (proto1), Expansion – Altera Nios Development Board User Manual

Page 19

Altera Corporation

1–11

December 2004

Nios Development Board Reference Manual, Cyclone Edition

Board Components

The Nios II factory-programmed reference design identifies these SRAM

devices in its address space as a contiguous 1Mbyte, 32-bit-wide,

zero-wait-state main memory.

The SRAM devices share address and data connections with the flash

memory and the Ethernet MAC/PHY device. For shared bus

information, see

“Shared Bus Table” on page A–1

f

See www.idt.com for detailed information about the SRAM devices.

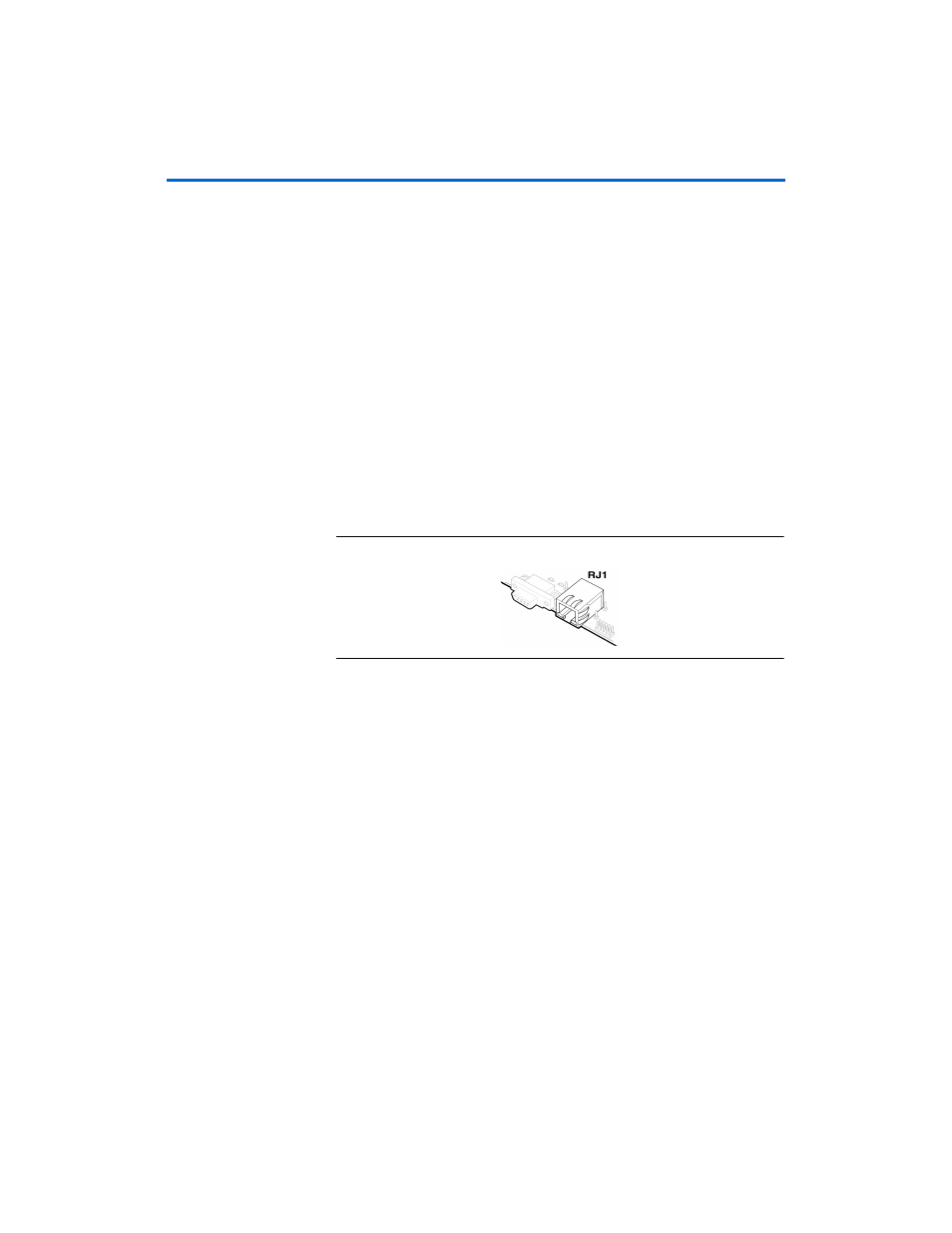

Ethernet

MAC/PHY

The LAN91C111 (U4) is a mixed-signal analog/digital device that

implements protocols at 10 Mbps and 100 Mbps. The control pins of U4

are connected to the Cyclone device so that Nios II systems can access

Ethernet via the RJ-45 connector (RJ1). See

. The Nios II

development kit includes hardware and software components that allow

Nios II processor systems to communicate with the LAN91C111 Ethernet

device.

Figure 1–4. Ethernet RJ-45 Connector

The Ethernet MAC/PHY device shares address and data connections

with the flash memory and the SRAM chips. For shared bus information,

see

“Shared Bus Table” on page A–1

f

See www.smsc.com

for detailed information about the LAN91C111

device.

Expansion

Prototype

Connector

(PROTO1)

The PROTO1 expansion prototype connectors share Cyclone I/O pins

with the CompactFlash connector. Designs may use either the PROTO1

connectors or the CompactFlash.

Headers J11, J12, and J13

collectively form the standard-footprint,

mechanically-stable connection that can be used (for example) as an

interface to a special-function daughter card.

f

See the Altera web site for a list of available expansion daughter cards

that can be used with the Nios development board at

www.altera.com/devkits

.