Altera Parallel Flash Loader IP User Manual

Page 38

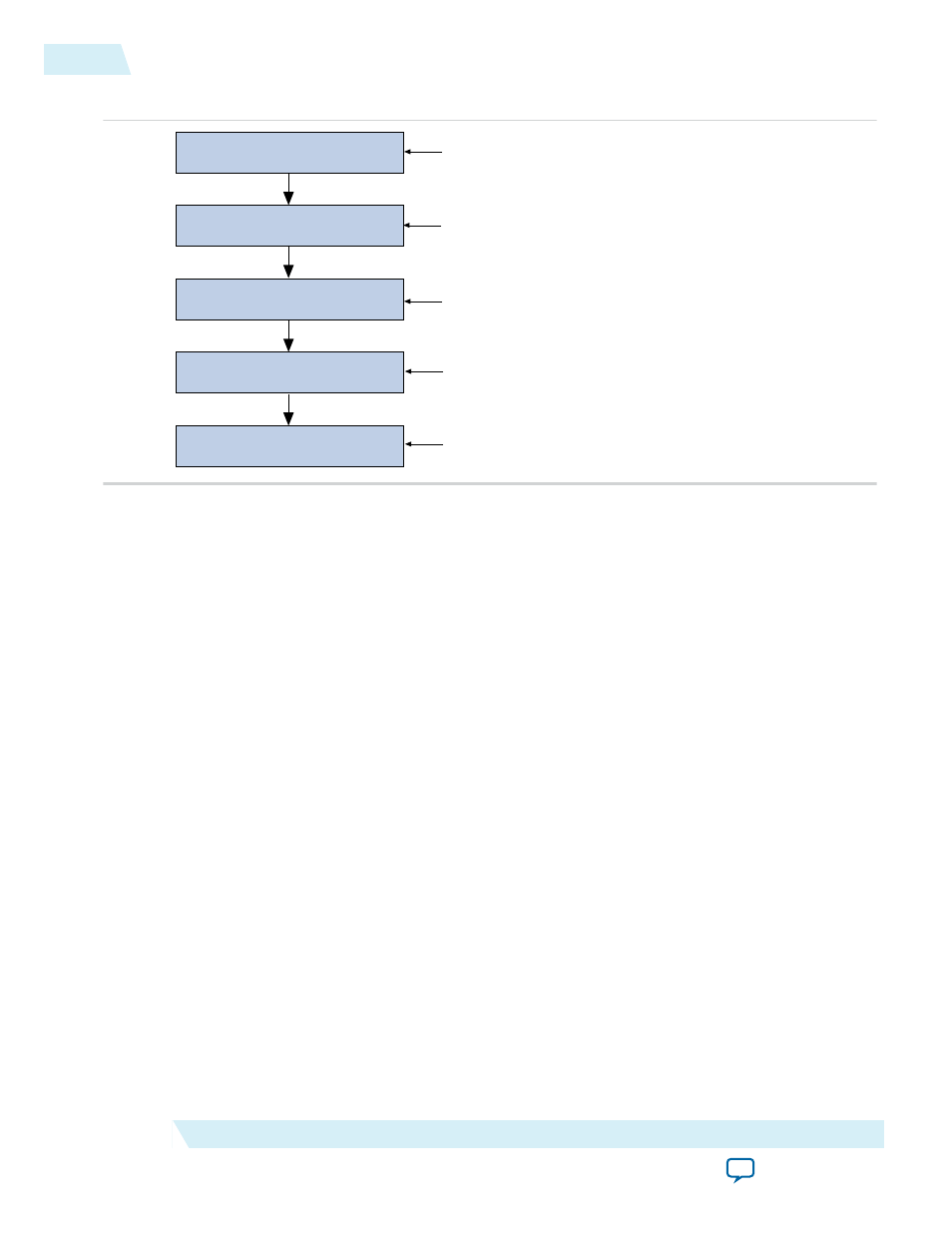

Figure 25: Nios II Processor and PFL Accessing the Flash Memory Device Sequence

Nios II processor connects

to the flash device

The PFL megafunction pulls the pfl_flash_access_request pin high

to request access to the flash device.

PFL megafunction requests

access to flash device

Nios II processor releases

the flash device

PFL megafunction accesses

the flash device

PFL megafunction releases

the flash device

By default, the Nios II processor is connected to the flash device.

All PFL megafunction output pins are tri-stated.

The Nios II processor tri-states all output pins to the flash device and routes

the output of pfl_flash_access_request to pfl_flash_access _granted.

The PFL megafunction accesses the flash device after receiving

a high input at the pfl_flash_access_granted input pin.

The pfl_flash_access_request pin stays high as long as

the PFL megafunction is connected to the flash device.

The PFL megafunction pulls the pfl_flash_access_request output pin low

after accessing the flash device.

Note: Altera recommends that you enable the safe state machine setting to prevent the PFL IP core from

entering an undefined state. To set this option, on the Assignments menu, click Settings. In the

Settings dialog box, on the Analysis and Synthesis page, click More Settings, and select safe state

machine.

The Altera CPLD and Nios II processor can each program the CFI flash memory device individually. To

prevent both processors from accessing the CFI flash memory device at the same time, the

flash_access_granted and flash_access_request pins of the CPLD and Nios II processor are connected

together.

To use other processors or controllers in place of the Nios II processor, ensure that the

pfl_flash_access_granted

and

pfl_flash_access_request

pins of the PFL IP core connect to your

processor using the method in

pfl_flash_access_request

and

pfl_flash_access_granted

Pins With

the Nios II and PFL IP Core table above.

You must also specify the flash memory device read or write access time for your processor or controller.

To avoid data contention when the PFL IP core is accessing the flash memory device, ensure that the

output pins from your processor are tri-stated when the

pfl_flash_access_request

signal is high.

Related Information

Provides more information about the Nios II processor.

38

PFL IP Core In Embedded Systems

UG-01082

2015.01.23

Altera Corporation

Parallel Flash Loader IP Core User Guide