Hsdi – Altera PowerPlay Early Power Estimator User Manual

Page 29

Altera Corporation

3–13

October 2005

PowerPlay Early Power Estimator User Guide: Stratix, Stratix GX & Cyclone FPGAs

Using PowerPlay Early Power Estimator for Stratix, Stratix GX & Cyclone FPGAs

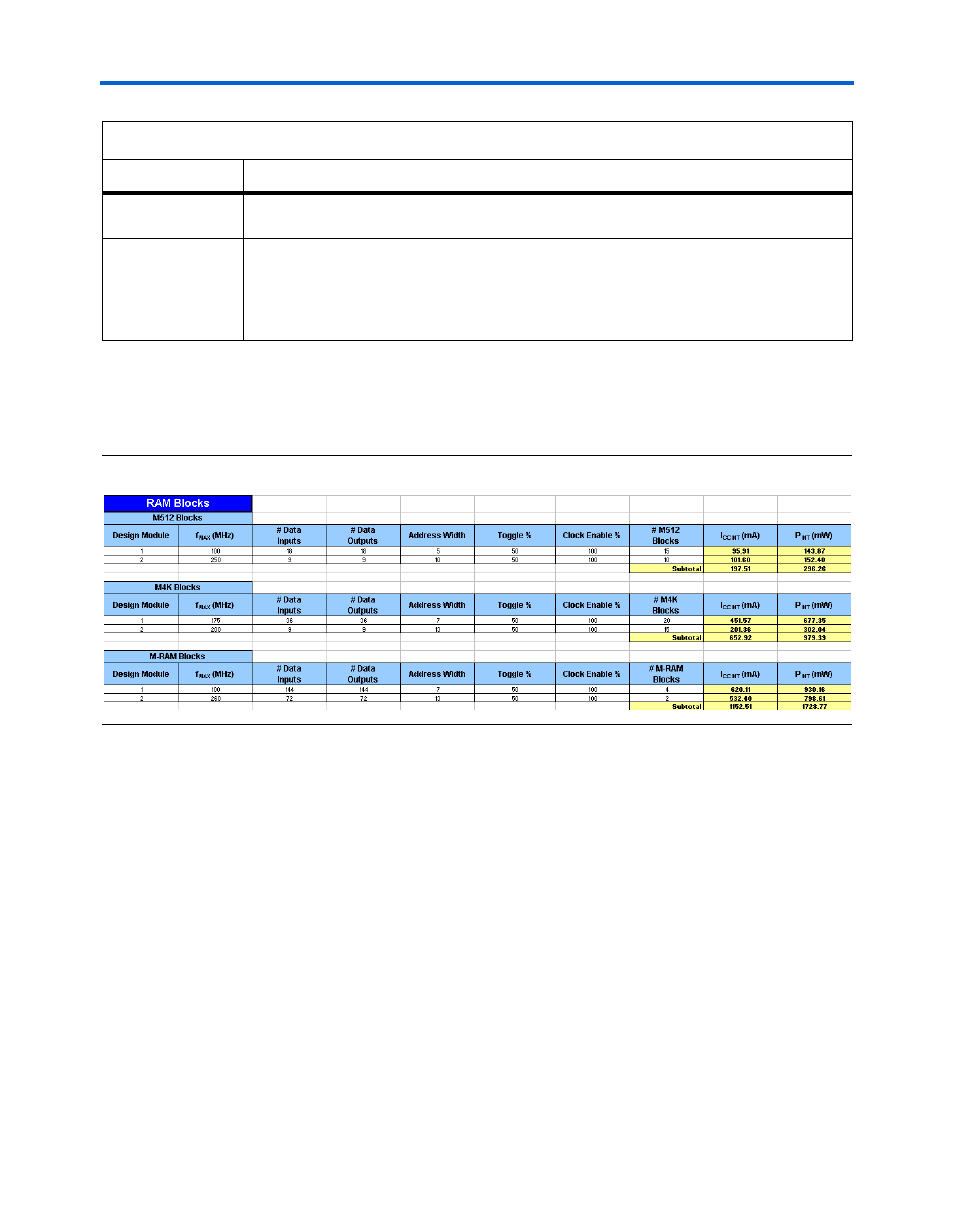

shows the Stratix device PowerPlay early power estimator

and the estimated power consumed by the RAM blocks for a design

targeting a Stratix device.

Figure 3–12. RAM Blocks Section in the Stratix PowerPlay Early Power Estimator

HSDI

The HSDI section is only found in the Stratix device PowerPlay early

power estimator. Stratix devices contain dedicated circuitry that supports

interfacing with high-speed differential I/O standards at speeds up to

840 megabits per second (Mbps). Stratix devices support the

HyperTransport technology, LVDS, LVPECL, and 3.3-V PCML

differential I/O standards. The HSDI section in the Stratix device

PowerPlay early power estimator is divided into two parts: Receiver and

Transmitter.

Each row in the HSDI section represents a separate receiver or

transmitter domain. For each transmitter domain used, you need to enter

the data rate (in Mbps), the number of channels in that transmitter

Clock Enable %

Enter the average percentage of RAM clock enabled. The toggle percentage ranges from

0 to 100%. Typically, the toggle percentage is 100%.

# <type of RAM>

Blocks

Enter the number of M512, M4K or M-RAM blocks that are configured with the same clock

frequency, data inputs and outputs, toggle percentage and mode. This value is limited by

the number of RAM blocks available in the largest device in the family. Verify that the

number of RAM blocks entered does not exceed the number of RAM blocks available in

your target device. The PowerPlay early power estimator does not verify this.

Table 3–5. RAM Blocks Section Information (Part 2 of 2)

Column Heading

Description