Altera PowerPlay Early Power Estimator User Manual

Page 32

3–16

UG-FPGAPWRCAL-2.0

Altera Corporation

PowerPlay Early Power Estimator User Guide: Stratix, Stratix GX & Cyclone FPGAs

October 2005

PowerPlay Early Power Estimator Input Values

the serializer outputs, and the I/O standard used on the output pins.

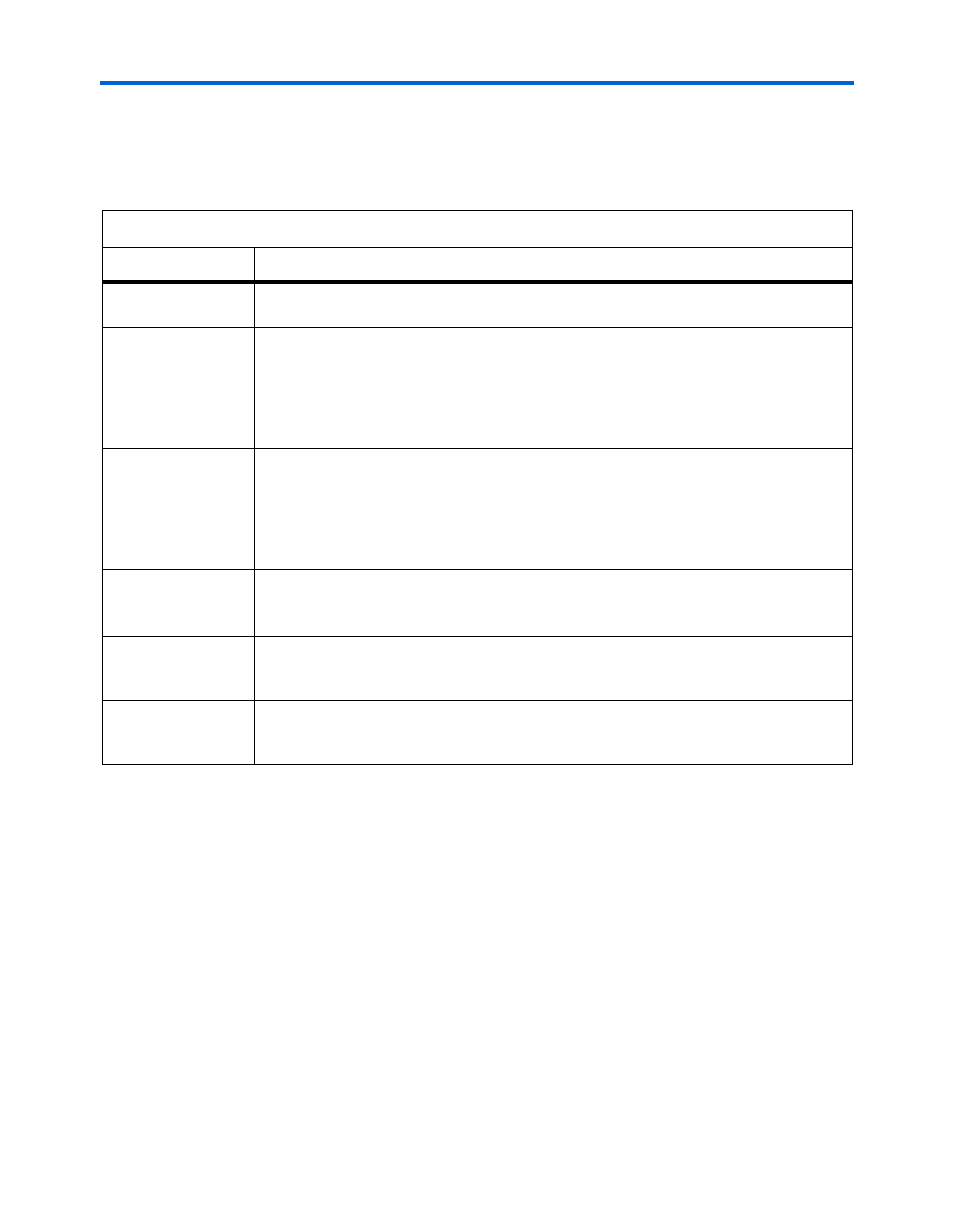

describes the values that are entered in the dedicated source-

synchronous circuitry section of the PowerPlay early power estimator.

shows the Stratix GX PowerPlay early power estimator and

the estimated power consumed by the dedicated source-synchronous

circuitry for a design targeting a Stratix GX device that has 10 LVDS

receiver (with DPA on) and transmitter channels operating at 1 Gbps

with data output toggling at 25%.

1

The power of the receiver and transmitter PLLs used by the

dedicated source synchronous circuitry is included in the

dedicated source-synchronous circuitry section. You do not

need to estimate the receiver and transmitter PLL power in the

PLL section.

Table 3–7. Dedicated Source-Synchronous Circuitry Section Information

Column Heading

Description

Domain

Enter a name for the receiver or transmitter domain in this column. This is an optional

value.

Data Rate (Mbps)

Enter the maximum data rate in Mbps of the receiver or transmitter channels for every

receiver and transmitter domain. If the design bypasses the DPA circuitry, Stratix GX

SERDES circuitry can receive data at rates up to 840 Mbps. If the design uses DPA

circuitry, Stratix GX SERDES circuitry can receive data at rates up to 1,000 Mbps

(1 Gbps). Stratix GX SERDES circuitry can transmit data up to 1,000 Mbps (1 Gbps).

Therefore, the data rate must be a decimal number from 0 to 1,000 Mbps.

# of Channels

Enter the number of receiver and transmitter channels running at the specified data rate.

For transmitters and receivers with DPA bypassed, each fast PLL in Stratix GX devices

can support up to 20 high-speed differential channels. For receivers with DPA on, the

number of receiver channels can be up to 23. Therefore, the receiver number of channels

must be an integer value from 0 to 23, while the number of transmitter channels must be

an integer value from 0 to 20.

DPA On/Bypass

Choose On from the DPA On/Bypass drop-down menu if you are using the DPA feature;

Choose Bypass from the DPA On/Bypass drop-down menu if you are not using the DPA

feature.

Toggle %

Enter the toggle %, which is the average percentage of serializer outputs toggling at each

high speed clock cycle. The toggle % ranges from 0 to 100%. Typically, the toggle % is

25%. To be more conservative, you can use a higher toggle percentage.

I/O Standard

Select the differential I/O standards used by the transmitter channels from the list. The

differential I/O standards available for the transmitter channels are HyperTransport

technology, LVDS, LVPECL, and 3.3-V PCML.