Dedicated source-synchronous circuitry, Figure 3–13 – Altera PowerPlay Early Power Estimator User Manual

Page 31

Altera Corporation

3–15

October 2005

PowerPlay Early Power Estimator User Guide: Stratix, Stratix GX & Cyclone FPGAs

Using PowerPlay Early Power Estimator for Stratix, Stratix GX & Cyclone FPGAs

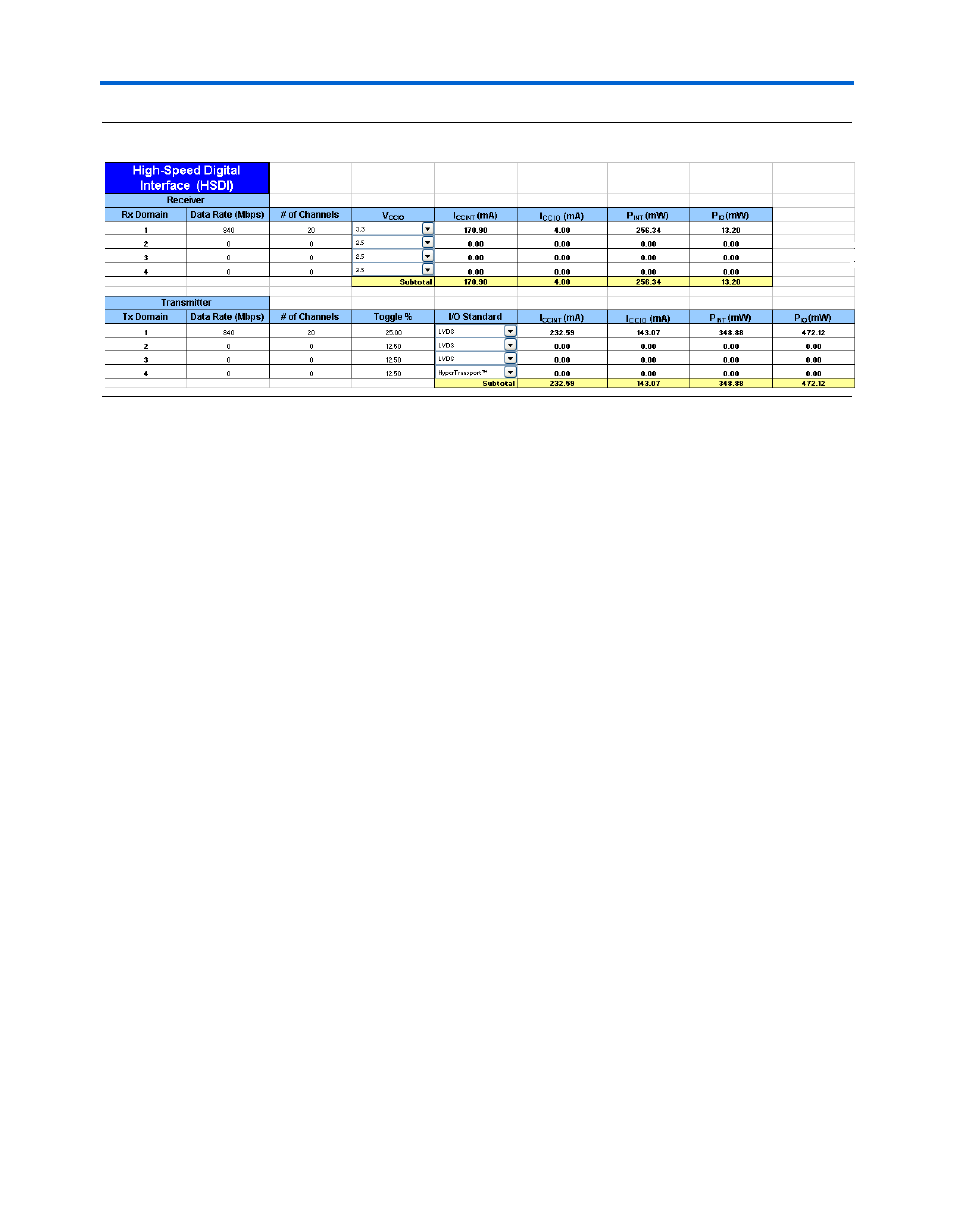

Figure 3–13. HSDI Section in the Stratix PowerPlay Early Power Estimator

Dedicated Source-Synchronous Circuitry

The Dedicated Source-Synchronous Circuitry section is only found in

the Stratix GX device PowerPlay early power estimator. The dedicated

source-synchronous circuitry in Stratix GX devices support a source-

synchronous high-speed interface and differential data rates up to

1 gigabit per second (Gbps). Stratix GX devices support the

HyperTransport technology, LVDS, LVPECL, and 3.3 V PCML

differential I/O standards. Each Stratix GX receiver channel features a

dynamic phase alignment (DPA) block. If you are using the DPA feature,

choose DPA On: If you are not using the DPA feature, choose Bypass

from the DPA On/Bypass drop-down menu. The dedicated

source-synchronous circuitry section in the Stratix GX PowerPlay early

power estimator is divided into two parts; Receiver and Transmitter.

Each row represents a separate receiver or transmitter domain. For each

receiver domain used, you need to enter the data rate (Mbps), the number

of channels in that receiver domain, and if DPA is on or bypassed. For

each transmitter domain used, you need to enter the data rate (Mbps), the

number of channels in that transmitter domain, the toggle percentage of