High-speed transceiver blocks, Figure 3–15, Figure 3–16 – Altera PowerPlay Early Power Estimator User Manual

Page 35

Altera Corporation

3–19

October 2005

PowerPlay Early Power Estimator User Guide: Stratix, Stratix GX & Cyclone FPGAs

Using PowerPlay Early Power Estimator for Stratix, Stratix GX & Cyclone FPGAs

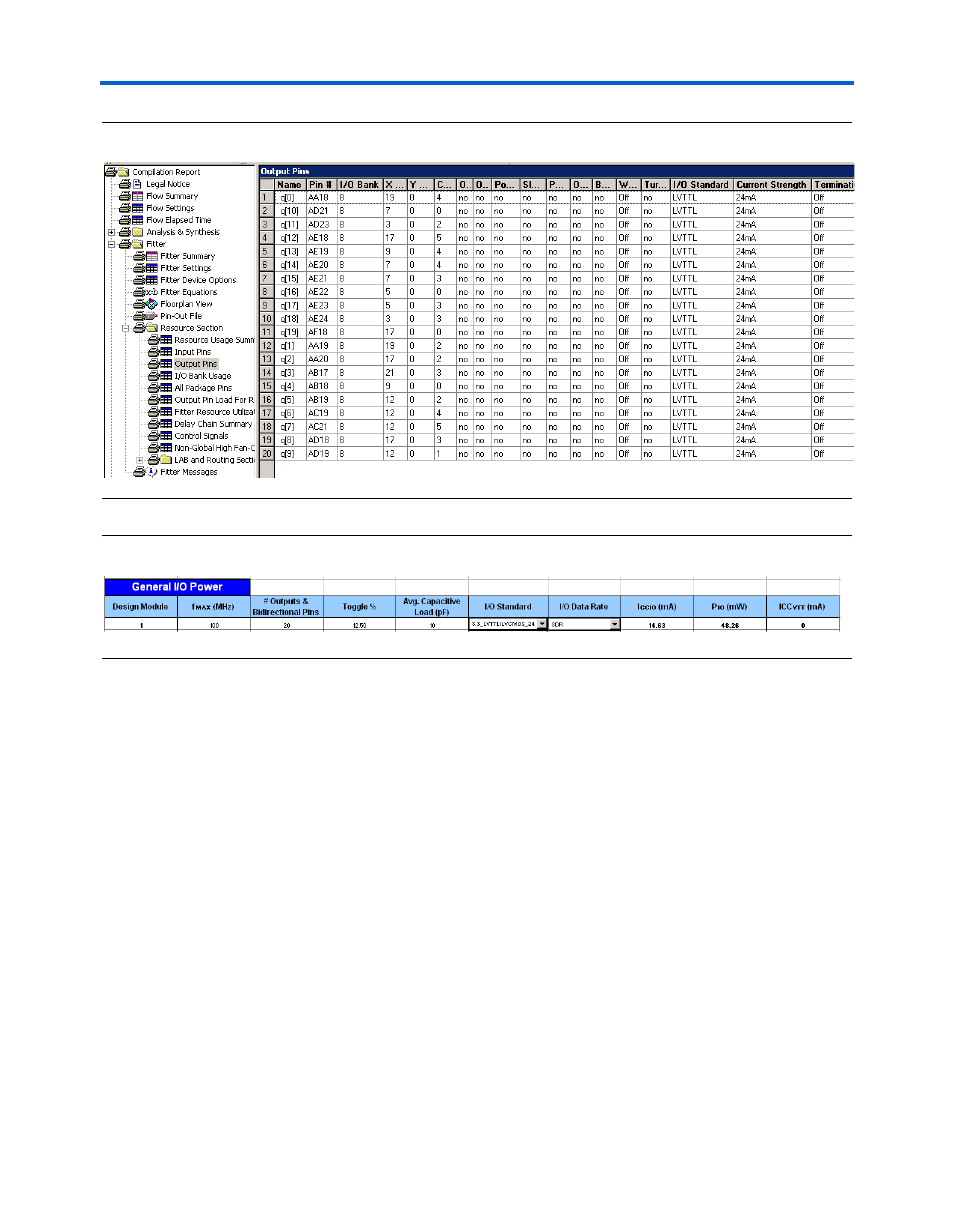

Figure 3–15. Output Pins Report in Compilation Report

Figure 3–16. General I/O Power Section in the Stratix PowerPlay Early Power Estimator

High-Speed Transceiver Blocks

The High-Speed Transceiver Blocks section is only found in the

Stratix GX device PowerPlay early power estimator. Stratix GX devices

contain transceivers that can receive and transmit data at rates up to

3.125 Gbps. Each transceiver block contains four channels, a transmit

PLL, four receive PLLs, and other control circuitry. The Stratix GX

transceiver blocks are located in I/O bank five. The total power

consumed by the transceiver blocks is reported as P

TRANSCEIVER

, which is

separate from P

INT

and P

IO

. The High-Speed Transceiver Blocks section

in the Stratix GX PowerPlay early power estimator is divided into

receiver and transmitter sections.

Each row represents a separate transceiver block. For each transceiver

block used on the receiving side, you need to enter the data rate (Gbps)

and the number of channels used. For each transceiver block used on the

transmitting side, you need to enter the data rate (Gbps), the number of

channels used, the toggle percentage of the serializer outputs, the

maximum output differential voltage (V

OD

), and the pre-emphasis