Csi/o baud rate selection – Zilog Z80180 User Manual

Page 165

Z8018x

Family MPU User Manual

150

UM005003-0703

After RESET, the CKS pin is configured as an external clock input (SS2,

SS1, SS0 = 1). Changing these values causes CKS to become an output pin

and the selected clock is output when transmit or receive operations are

enabled.

CSI/O Interrupts

The CSI/O interrupt request circuit is shown in Figure 58.

CSI/O Transmit/Receive Register (TRDR: 0BH)

Bit

7

6

5

4

3

2

1

0

Bit/Field

CSI/O Transmit/Receive Data

R/W

R/W

Reset

0

Note: R = Read W = Write X = Indeterminate ? = Not Applicable

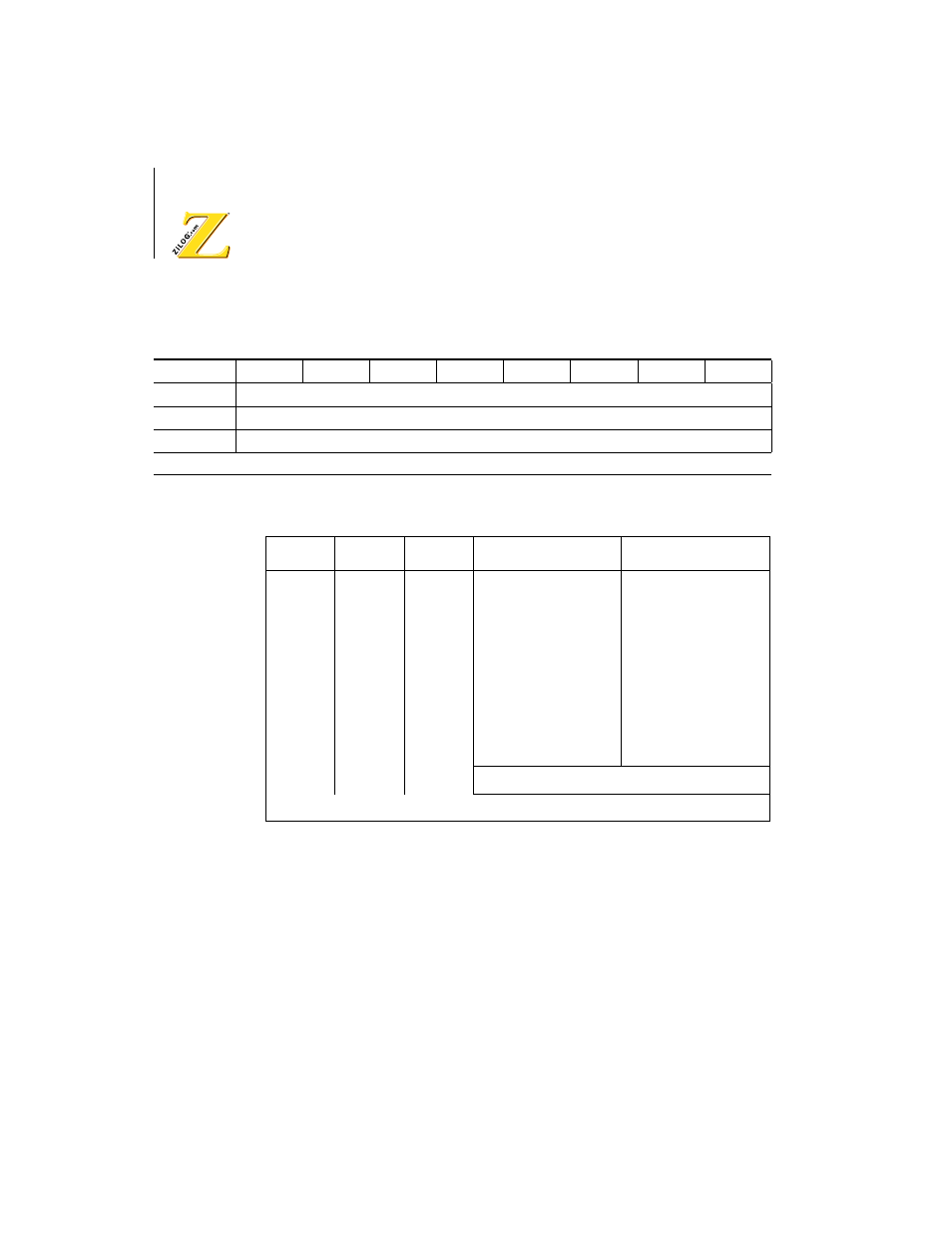

Table 22. CSI/O Baud Rate Selection

SS2

SS1

SS0

Divide Ratio

Baud Rate

0

0

0

¸

20

(200000)

0

0

1

¸

40

(100000)

0

1

0

¸

80

(50000)

0

1

1

¸

160

(25000)

1

0

0

¸

320

(12500)

1

0

1

¸

640

(6250)

1

1

0

¸

1280

(3125)

1

1

1

External Clock input (less than

¸

20)

Note: ( ) indicates the baud rate (BPS) at Phi = 4 MHz.