Halt timing diagram – Zilog Z80180 User Manual

Page 48

Advertising

Z8018x

Family MPU User Manual

UM005003-0703

33

.

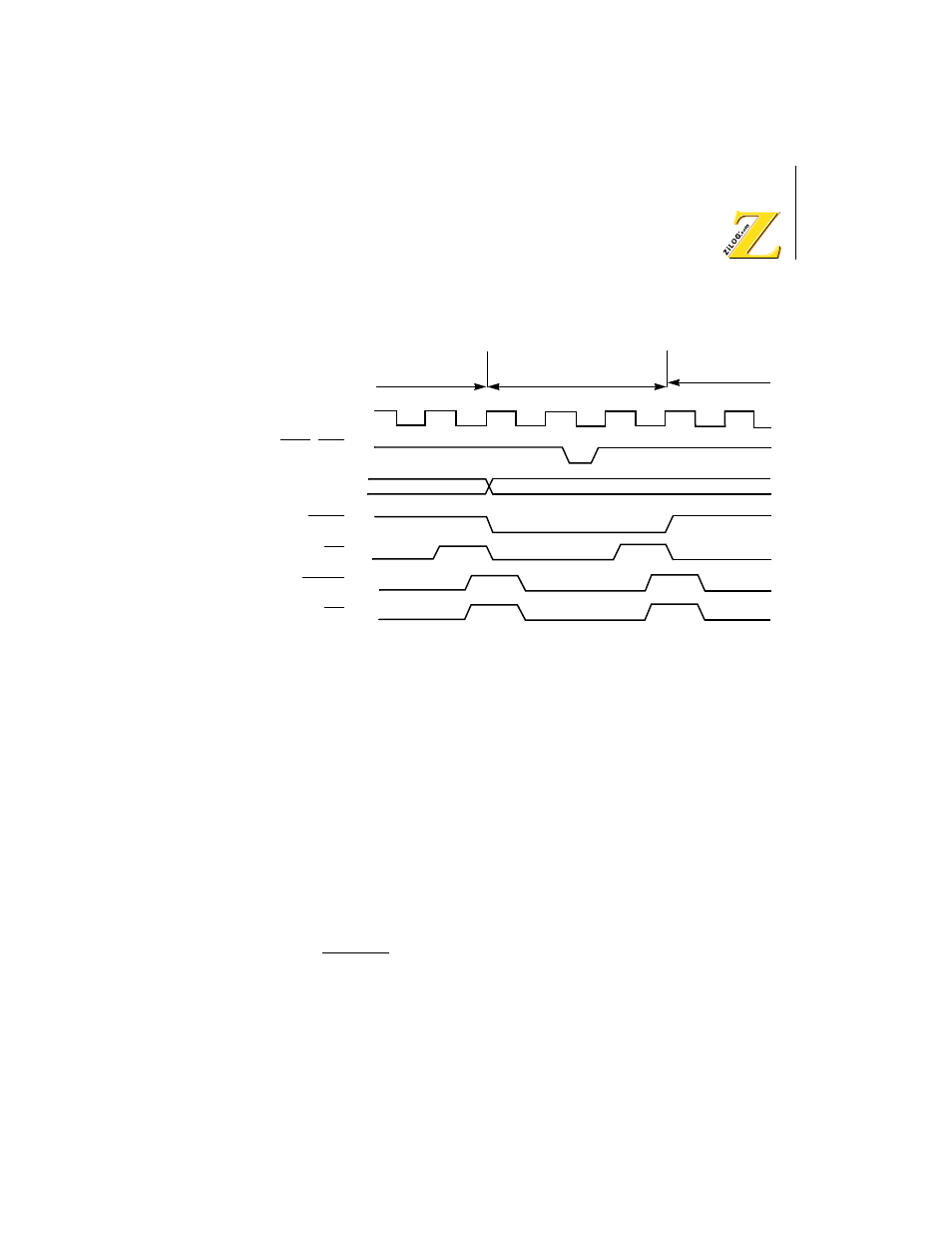

Figure 20. HALT Timing Diagram

SLEEP Mode

SLEEP mode is entered by execution of the 2-byte SLP instruction.

SLEEP mode contains the following characteristics:

•

The internal CPU clock stops, reducing power consumption

•

The internal crystal oscillator does not stop

•

Internal and external interrupt inputs can be received

•

DRAM refresh cycles stop

•

I/O operations using on-chip peripherals continue

•

The internal DMAC stop

•

BUSREQ can be received and acknowledged

•

Address outputs go High and all other control signal outputs become

inactive High

T1

M1

RD

MREQ

Phi

A0

–

A19

INT1, NMI

T3

T1

T2

T3

T1

T2

HALT Op Code

HALT mode

Interrupt

acknowledge cycle

HALT

HALT Op Code address

HALT Op Code address + 1

Fetch Cycle

Advertising