User watchdog timer, Altera dual configuration ip core – Altera MAX 10 FPGA User Manual

Page 18

User Watchdog Timer

The user watchdog timer prevents a faulty application configuration from stalling the device indefinitely.

You can use the timer to detect functional errors when an application configuration is successfully loaded

into the device.

The counter is 29 bits wide and has a maximum count value of 2

29

. When specifying the user watchdog

timer value, specify only the most significant 12 bits. The granularity of the timer setting is 2

17

cycles. The

cycle time is based on the frequency of the user watchdog timer internal oscillator. Depending on the

counter and the internal oscillator of the device, you can set the cycle time from 9ms to 244s.

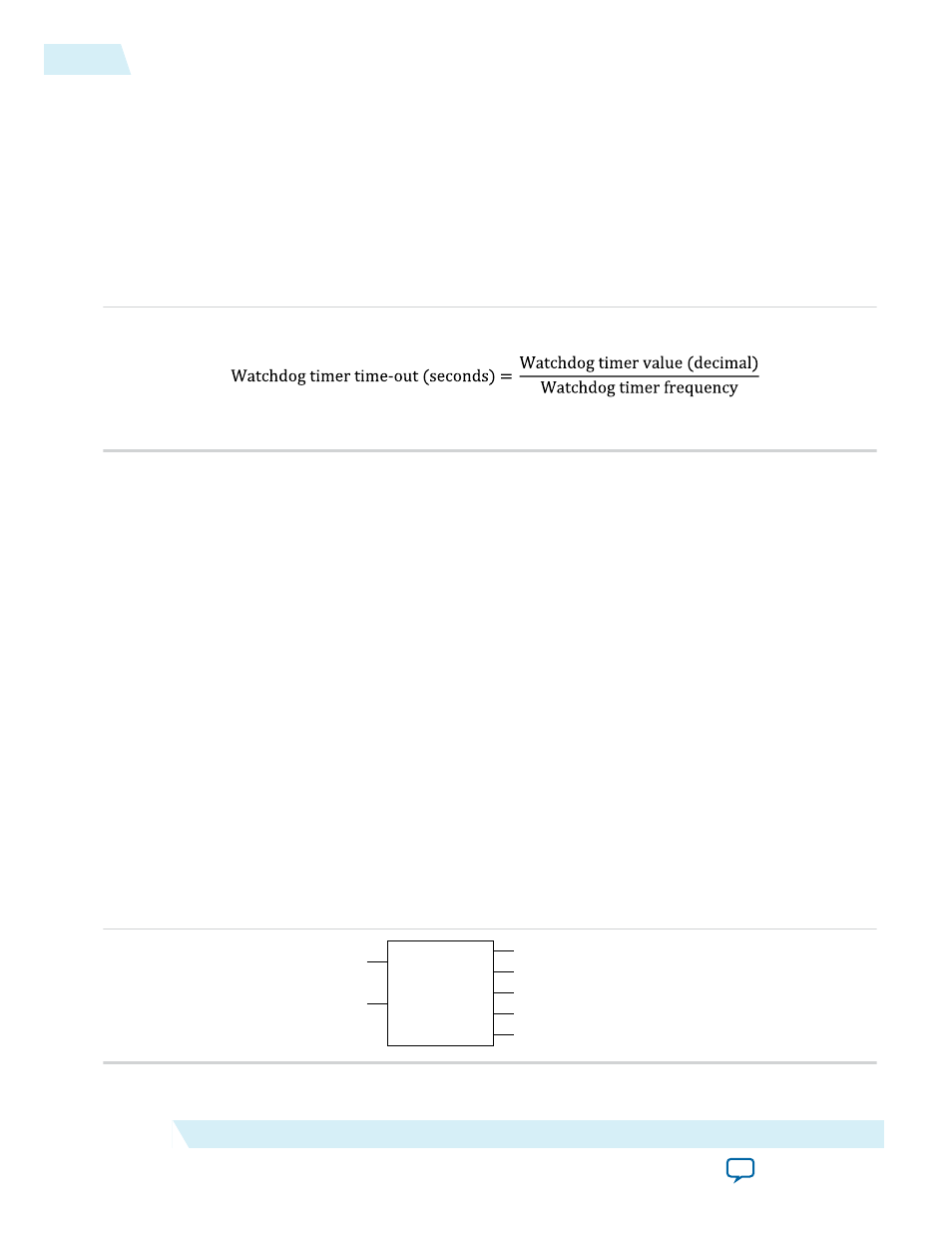

Figure 2-5: Watchdog Timer Formula for MAX 10 Devices

The timer begins counting as soon as the application configuration enters user mode. When the timer

expires, the remote system upgrade circuitry generates a time-out signal, updates the status register, and

triggers the loading of the revert configuration image. To reset the timer, pulse the

RU_NRSTIMER

for a

minimum of 250 ns.

When you enable the watchdog timer, the setting will apply to all images, all images should contain the

soft logic configuration to reset the timer. Application Configuration will reset the control block registers.

Related Information

•

Provides more information about the user watchdog frequency.

•

Initialization Configuration Bits

Altera Dual Configuration IP Core

The Altera Dual Configuration IP core offers the following capabilities through Avalon-MM interface:

• Asserts

RU_nCONFIG

to trigger reconfiguration.

• Asserts

RU_nRSTIMER

to reset watchdog timer if the watchdog timer is enabled.

• Writes configuration setting to the input register of the remote system upgrade circuitry.

• Reads information from the remote system upgrade circuitry.

Figure 2-6: Altera Dual Configuration IP Core Block Diagram

Altera

Dual Configuration

clk

nreset

avmm_rcv_address[2..0]

avmm_rcv_read

avmm_rcv_writedata[31..0]

avmm_rcv_write

avmm_rcv_readdata[31..0]

2-14

User Watchdog Timer

UG-M10CONFIG

2015.05.04

Altera Corporation

MAX 10 FPGA Configuration Schemes and Features