Change_edreg jtag instruction, Error detection timing, Error detection frequency – Altera MAX 10 FPGA User Manual

Page 24

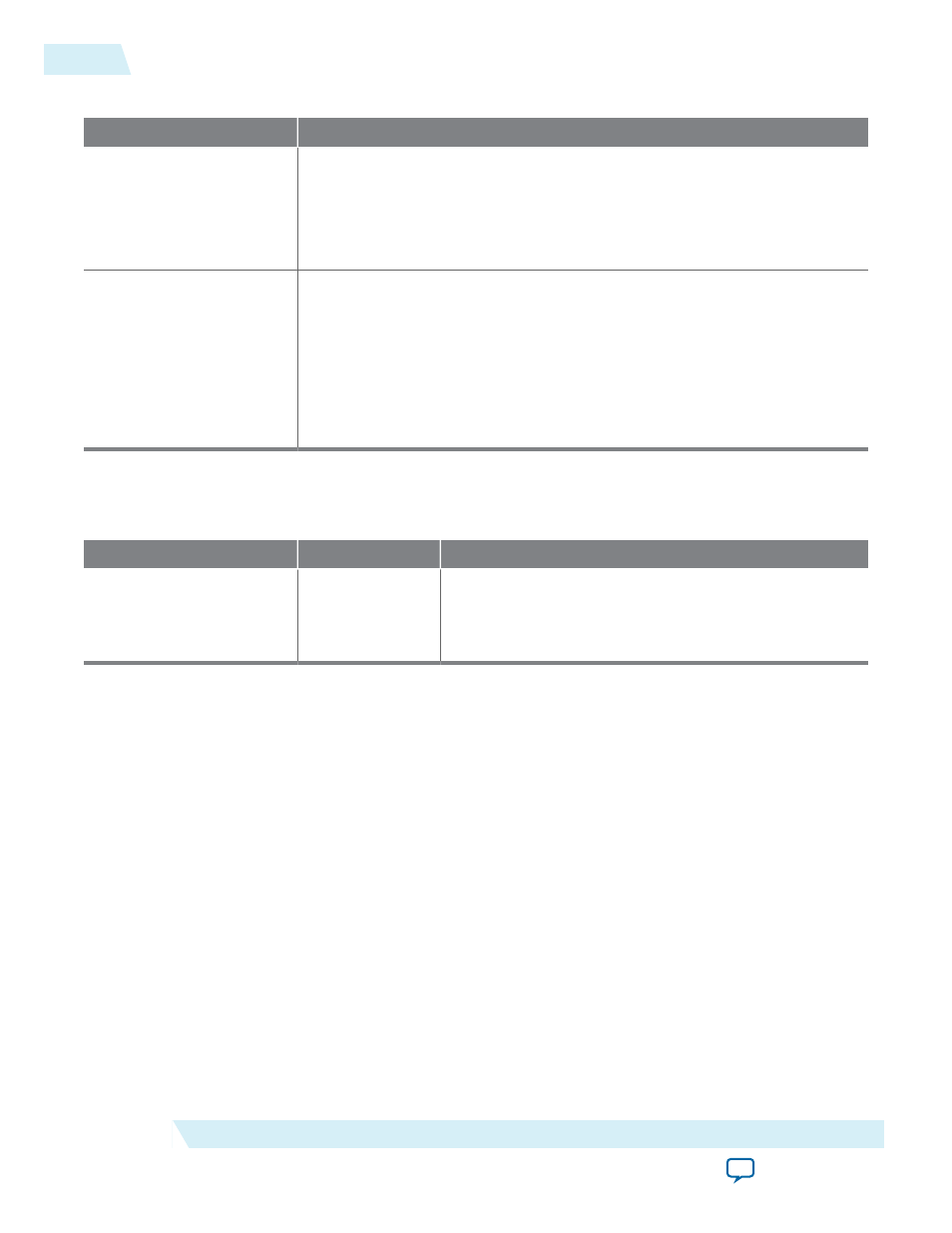

Table 2-15: Error Detection Registers for MAX 10 Devices

Register

Description

32-bit signature register

This register contains the CRC signature. The signature register contains the

result of the user mode calculated CRC value compared against the pre-

calculated CRC value. If no errors are detected, the signature register is all

zeroes. A non-zero signature register indicates an error in the configuration

CRAM contents. The

CRC_ERROR

signal is derived from the contents of this

register.

32-bit storage register

This register is loaded with the 32-bit pre-computed CRC signature at the end

of the configuration stage. The signature is then loaded into the 32-bit

Compute and Compare CRC block during user mode to calculate the CRC

error. This register forms a 32-bit scan chain during execution of the

CHANGE_

EDREG

JTAG instruction. The

CHANGE_EDREG

JTAG instruction can change the

content of the storage register. Therefore, the functionality of the error

detection CRC circuitry is checked in-system by executing the instruction to

inject an error during the operation. The operation of the device is not halted

when issuing the

CHANGE_EDREG

JTAG instruction.

CHANGE_EDREG JTAG Instruction

Table 2-16:

CHANGE_EDREG

JTAG Instruction Description

JTAG Instruction

Instruction Code

Description

CHANGE_EDREG

00 0001 0101

This instruction connects the 32-bit CRC storage register

between

TDI

and

TDO

. Any precomputed CRC is loaded

into the CRC storage register to test the operation of the

error detection CRC circuitry at the

CRC_ERROR

pin.

Error Detection Timing

When the error detection CRC feature is enabled through the Quartus II software, the device

automatically activates the CRC process upon entering user mode, after configuration and initialization is

complete.

The

CRC_ERROR

pin will remain low until the error detection circuitry has detected a corrupted bit in the

previous CRC calculation. After the pin goes high, it remains high during the next CRC calculation. This

pin does not log the previous CRC calculation. If the new CRC calculation does not contain any corrupted

bits, the

CRC_ERROR

pin is driven low. The error detection runs until the device is reset.

The error detection circuitry is clocked by an internal configuration oscillator with a divisor that sets the

maximum frequency. The CRC calculation time depends on the device and the error detection clock

frequency.

Related Information

Error Detection Frequency

You can set a lower clock frequency by specifying a division factor in the Quartus II software.

2-20

CHANGE_EDREG JTAG Instruction

UG-M10CONFIG

2015.05.04

Altera Corporation

MAX 10 FPGA Configuration Schemes and Features