Real-time isp, Isp and real-time isp instructions – Altera MAX 10 FPGA User Manual

Page 9

The following are the generic flow of an ISP operation:

1. Check ID—the JTAG ID is checked before any program or verify process. The time required to read

this JTAG ID is relatively small compared to the overall programming time.

2. Enter ISP—ensures the I/O pins transition smoothly from user mode to the ISP mode.

3. Sector Erase—shifting in the address and instruction to erase the device and applying erase pulses.

4. Program—shifting in the address, data, and program instructions and generating the program pulse to

program the flash cells. This process is repeated for each address in the internal flash sector.

5. Verify—shifting in addresses, applying the verify instruction to generate the read pulse, and shifting

out the data for comparison. This process is repeated for each internal flash address.

6. Exit ISP—ensures that the I/O pins transition smoothly from the ISP mode to the user mode.

You can also use the Quartus II Programmer to program the CFM.

Related Information

Programming .pof into Internal Flash

Provides the steps to program the .pof using Quartus II Programmer.

Real-Time ISP

In a normal ISP operation, to update the internal flash with a new design image, the device exits from user

mode and all I/O pins remain tri-stated. After the device completes programing the new design image, it

resets and enters user mode.

The real-time ISP feature updates the internal flash with a new design image while operating in user

mode. During the internal flash programming, the device continues to operate using the existing design.

After the new design image programming process completes, the device will not reset. The new design

image update only takes effect in the next reconfiguration cycle.

ISP and Real-Time ISP Instructions

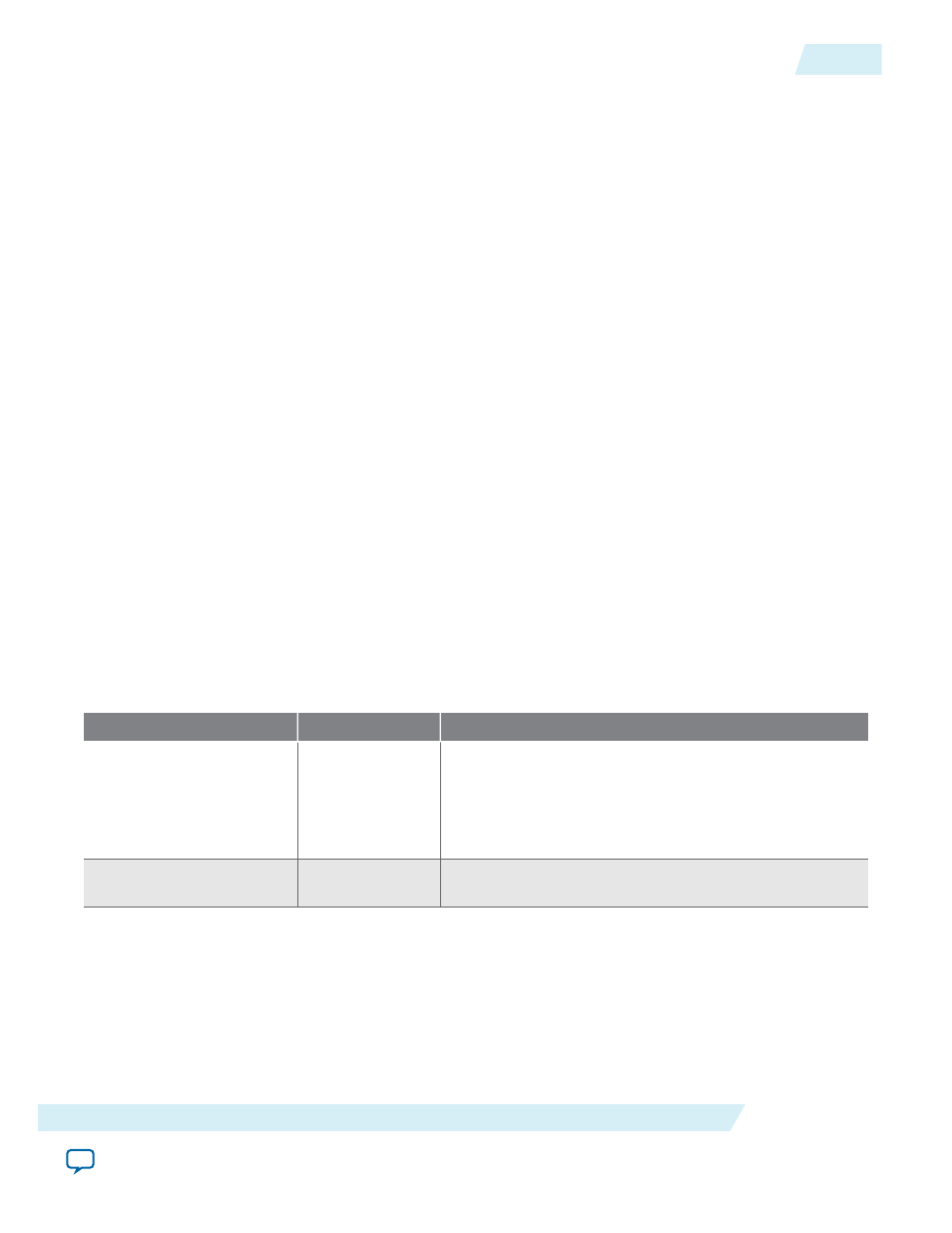

Table 2-4: ISP and Real-Time ISP Instructions for MAX 10 Devices

Instruction

Instruction Code

Description

CONFIG_IO

00 0000 1101

• Allows I/O reconfiguration through JTAG ports using

the IOCSR for JTAG testing. This is executed after or

during configurations.

•

nSTATUS

pin must go high before you can issue the

CONFIG_IO

instruction.

PULSE_NCONFIG

00 0000 0001

Emulates pulsing the

nCONFIG

pin low to trigger reconfi‐

guration even though the physical pin is unaffected.

UG-M10CONFIG

2015.05.04

Real-Time ISP

2-5

MAX 10 FPGA Configuration Schemes and Features

Altera Corporation