Pll reconfiguration with multiple .mif files – Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 23

Design Example

Page 23

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

PLL Reconfiguration with Multiple .mif Files

This design example uses the ALTPLL_RECONFIG megafunction to reconfigure the

output of the

c0

counter based on the PLL settings specified in multiple .mif files from

external ROMs in Stratix III devices. The .mif files specify PLL settings that

reconfigure the output of the

c0

counter from 100 to 200 MHz, 300 MHz, 400 MHz,

and 500 MHz, then back to 200 MHz.

Generating the ALTPLL and ALTPLL_RECONFIG Megafunctions

To generate the ALTPLL and ALTPLL_RECONFIG megafunctions, follow these steps:

1. Open the ALTPLL_RECONFIG_DesignExample_ex3.zip

file to any directory on

your PC.

2. Open the ALTPLL_RECONFIG_rom.qar project file.

3. On the Tools menu, click MegaWizard Plug-In Manager. Page 1 of the

MegaWizard Plug-In Manager appears.

4. Select the Create a new custom megafunction variation option.

5. Click Next. Page 2a of the MegaWizard Plug-In Manager appears.

6. In the MegaWizard Plug-In Manager pages, select or verify the configuration

settings listed in

. Click Next to advance from one page to the next.

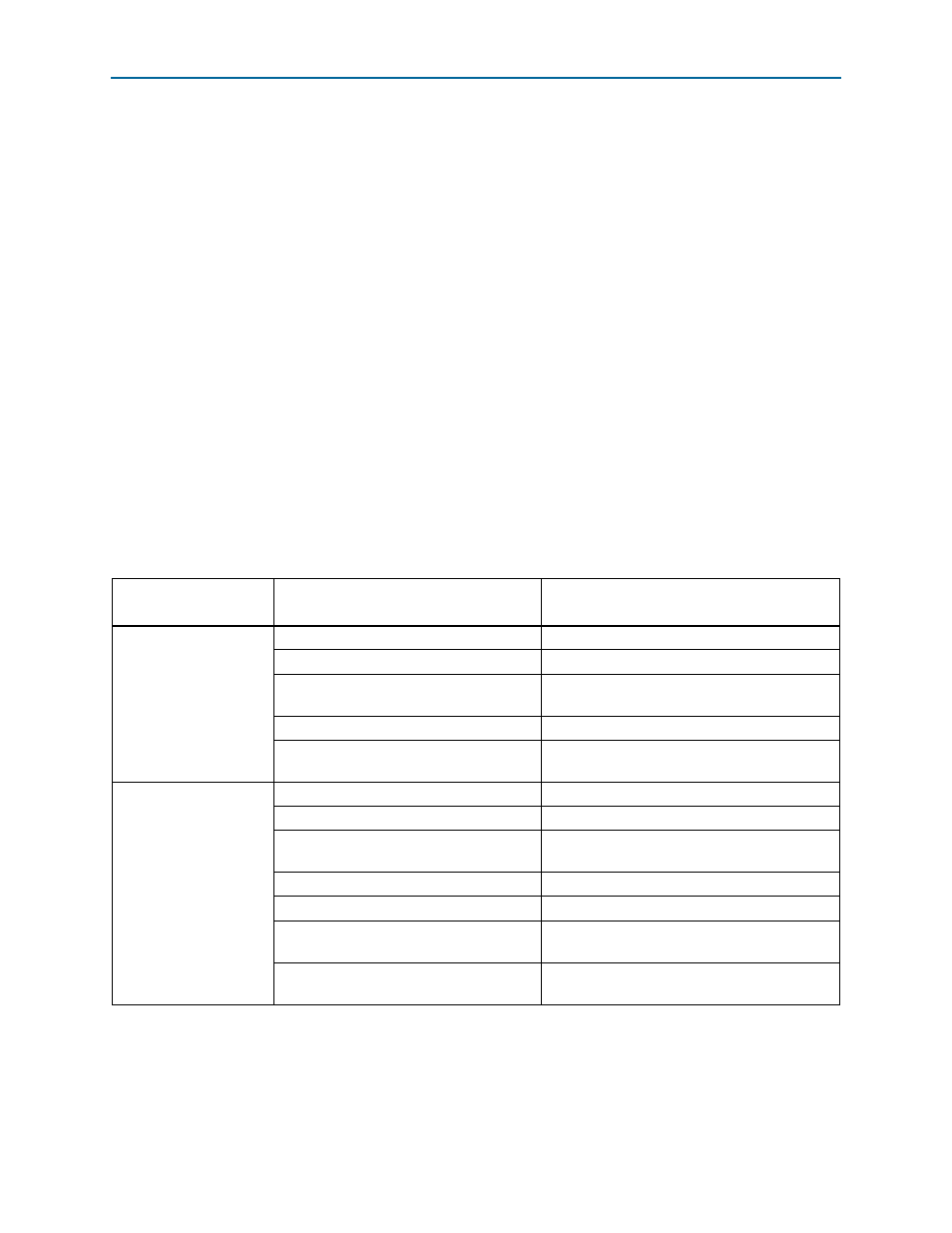

Table 6. Configuration Settings for the ALTPLL Megafunction (Part 1 of 2)

MegaWizard Plug-In

Manager Page

Settings

Value

2a

Megafunction

Under the I/O category, select ALTPLL

Which device family will you be using?

Stratix III

Which type of output file do you want to

create?

Verilog

What name do you want for the output file?

the_pll.v

Return to this page for another create

operation

Turned on

Parameter Settings

(General/Modes)

Currently selected device family

Stratix III

Match project/default

Turned on

Which device speed grade will you be

using?

Any

What is the frequency of inclk0 input

50 MHz

Which PLL type will you be using?

Top_Bottom PLL

How will the PLL outputs be generated?

Select Use the feedback path inside the PLL.

Select In normal mode

Which output clock will be compensated

for?

c0