Figure 30 – Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 35

Advertising

Design Example

Page 35

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

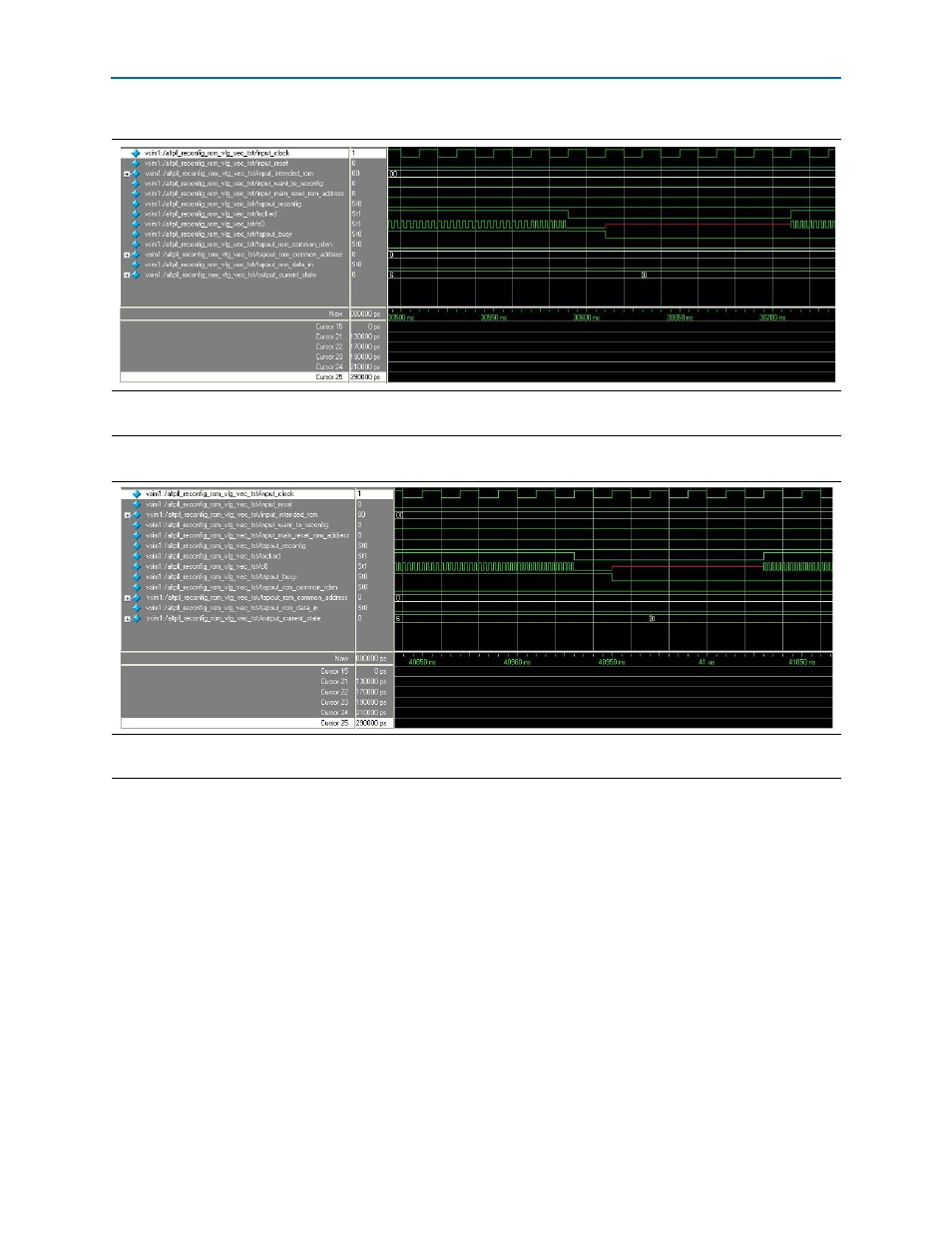

Figure 29. PLL Reconfiguration from ROM 3 (30,480 to 30,750 ns)

Note to

(1) From

c0

= 300 MHz to

c0

= 400 MHz.

Figure 30. PLL Reconfiguration from ROM 4 (40,800 to 41,090 ns)

Note to

(1) From

c0

= 400 MHz to

c0

= 500 MHz.

Advertising