Ports and parameters – Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 40

Page 40

Specifications

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

Ports and Parameters

This section describes the ports and parameters of the ALTPLL_RECONFIG

megafunction.

lists the ALTPLL_RECONFIG megafunction input ports.

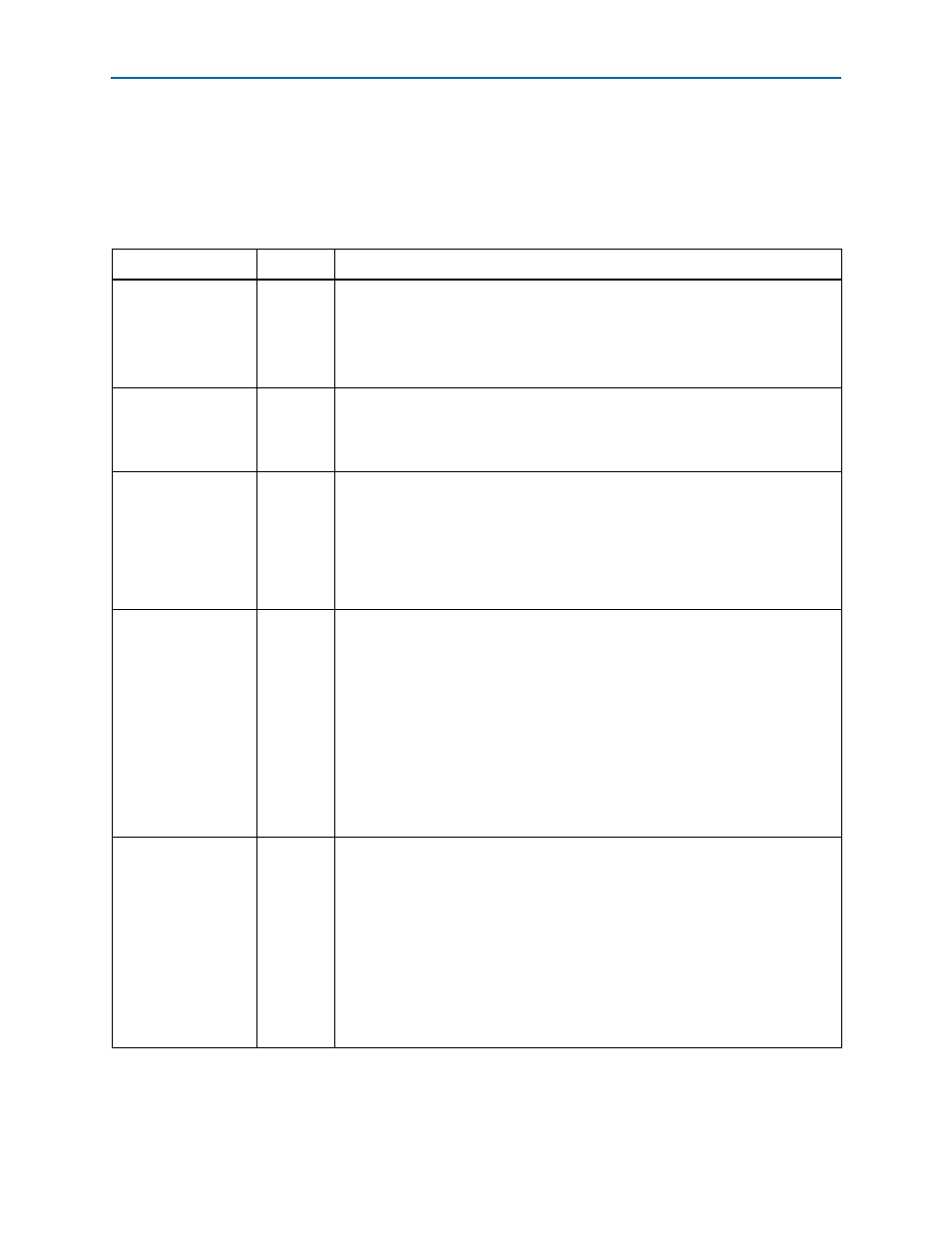

Table 8. ALTPLL_RECONFIG Megafunction Input Ports (Part 1 of 3)

Port Name

Required?

Description

clock

Yes

Clock input for loading individual parameters. This signal also clocks the PLL during

reconfiguration.

The clock input port must be connected to a valid clock.

Refer to the DC and Switching Characteristics chapter of the respective device

handbooks for the clock f

MAX

.

reset

Yes

Asynchronous reset input to the megafunction.

Altera recommends that you reset this megafunction before first use to guarantee that

it is in a valid state. However, it does power up in the reset state. This port must be

connected.

data_in[]

No

Data input that provides parameter value when writing parameters.

A 9-bit input port that provides the data to be written to the scan cache during a write

operation. The bit width of the counter parameter to be written determines the

number of bits of

data_in[]

that are read into the cache. For example, the low bit

count of the

C0

counter is 8-bit wide, so

data_in[7..0]

is read to the correct cache

location. The bypass mode for the C0 counter is 1-bit wide, so

data_in[0]

is read

for the value of this parameter. If omitted, the default value is

0

.

counter_type[]

No

Specifies the counter type.

An input port in the form of a 4-bit bus that selects which counter type should be

selected for the corresponding operation (

read

,

write

, or

reconfig

). The following

table specifies the mapping between the

counter_type

value and the physical

counter to be set. For details, refer to the following tables:

■

counter_type[3..0]

settings for Stratix III, Stratix IV, and

Cyclone III devices.

■

counter_type[3..0]

settings for Stratix II, Stratix II GX,

Arria GX and HardCopy II devices.

■

counter_type[3..0]

settings for Stratix and Stratix GX

devices.

counter_param[]

No

Specifies the parameter for the value specified in the

counter_type

port.

An input port in the form of a 3-bit bus that selects which parameter for the given

counter type should be updated. The mapping to each parameter type and the

corresponding parameter bit-width are defined in the following tables:

■

counter_param[2..0]

settings for Stratix III, Stratix IV, and

Cyclone III devices.

■

counter_param[2..0]

settings for Stratix II, Stratix II GX,

Arria GX and HardCopy II devices.

■

counter_param[2..0]

settings for Stratix and Stratix GX

devices.