Altera Phase-Locked Loop Reconfiguration IP Core User Manual

Page 47

Specifications

Page 47

Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) Megafunction

February 2012

Altera Corporation

lists the

counter_type

and

counter_param

settings for Stratix II,

Stratix II GX, Arria GX, and HardCopy II devices.

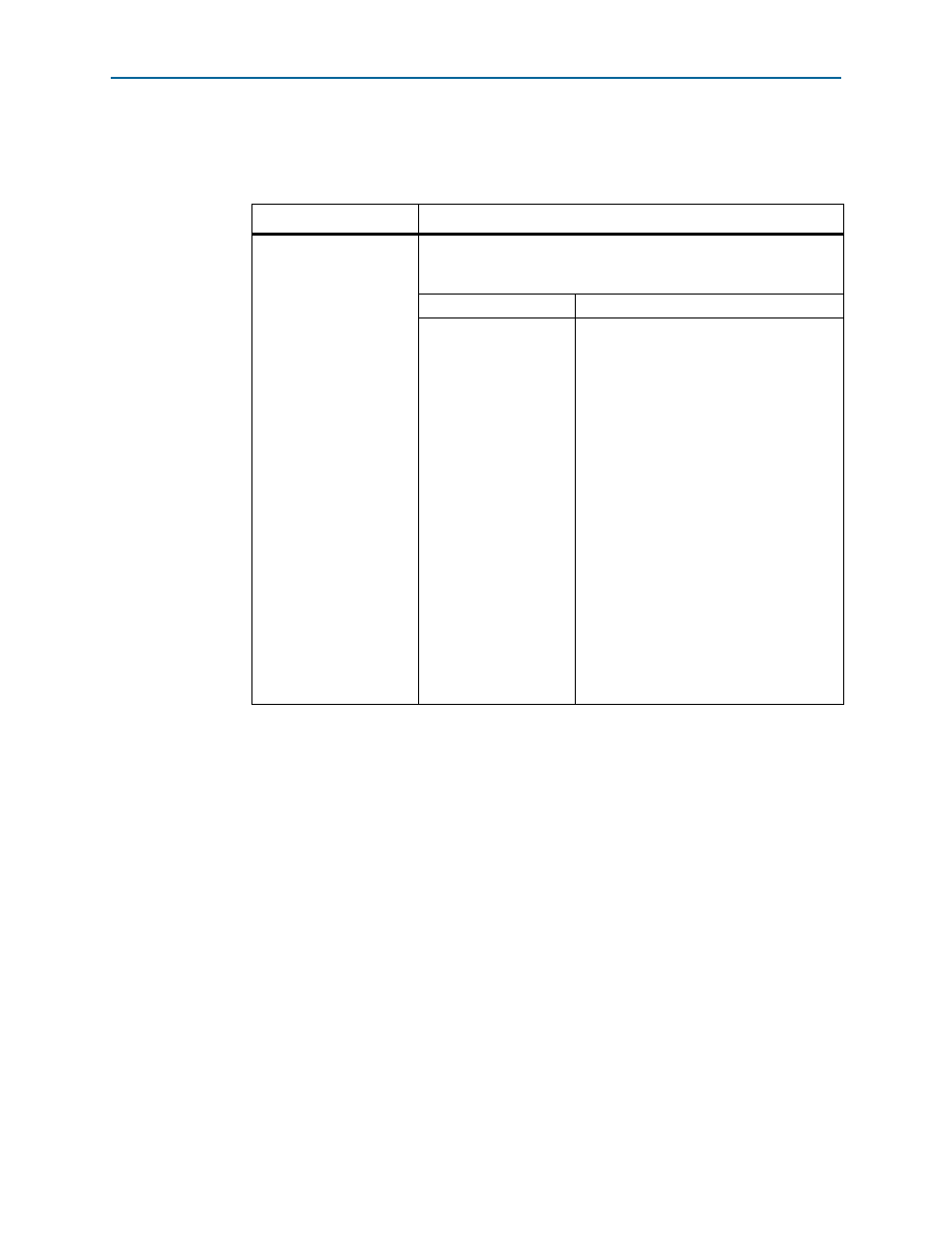

Table 13. counter_type and counter_param Settings for Stratix II, Stratix II GX, Arria GX, and

HardCopy II Devices (Part 1 of 2)

Counter

Settings

counter_type[]

4-bit bus that selects which counter type must be updated. The

following mapping determines which counter is specified for each

counter_type

value.

counter_type[3..0]

Selected Counter

0000 (0x0)

0001 (0x1)

0010 (0x2)

0011 (0x3)

0100 (0x4)

0101 (0x5)

0110 (0x6)

0111 (0x7)

1000 (0x8)

1001 (0x9)

1010 (0xA)

1011 (0xB)

1100 (0xC)

1101 (0xD)

1110 (0xE)

1111 (0xF)

N [Enhanced PLL/ Fast PLL]

M [Enhanced PLL/ Fast PLL]

P/LF [Enhanced PLL/ Fast PLL]

(Illegal value)

C0 [Enhanced PLL/ Fast PLL]

C1 [Enhanced PLL/ Fast PLL]

C2 [Enhanced PLL/ Fast PLL]

C3 [Enhanced PLL/ Fast PLL]

C4 [Enhanced PLL]

C5 [Enhanced PLL]

(Illegal value)

(Illegal value)

(Illegal value)

(Illegal value)

(Illegal value)

(Illegal value)