Nios ii 3c120 microprocessor with lcd controller, Cpu platform, The cpu platform consists of – Altera Embedded Systems Development Kit, Cyclone III Edition User Manual

Page 43: Nios ii/f cpu core, Jtag debug port, 32kb instruction cache, 32kb data cache, Ddr2 sdram controller, Cfi flash controller, Stores fpga configuration data

6–5

Development Board Version 1.0.

Altera Corporation

Altera Embedded Systems Development Kit, Cyclone III Edition

July 2010

About the Nios II 3C120 Microprocessor System with LCD Controller

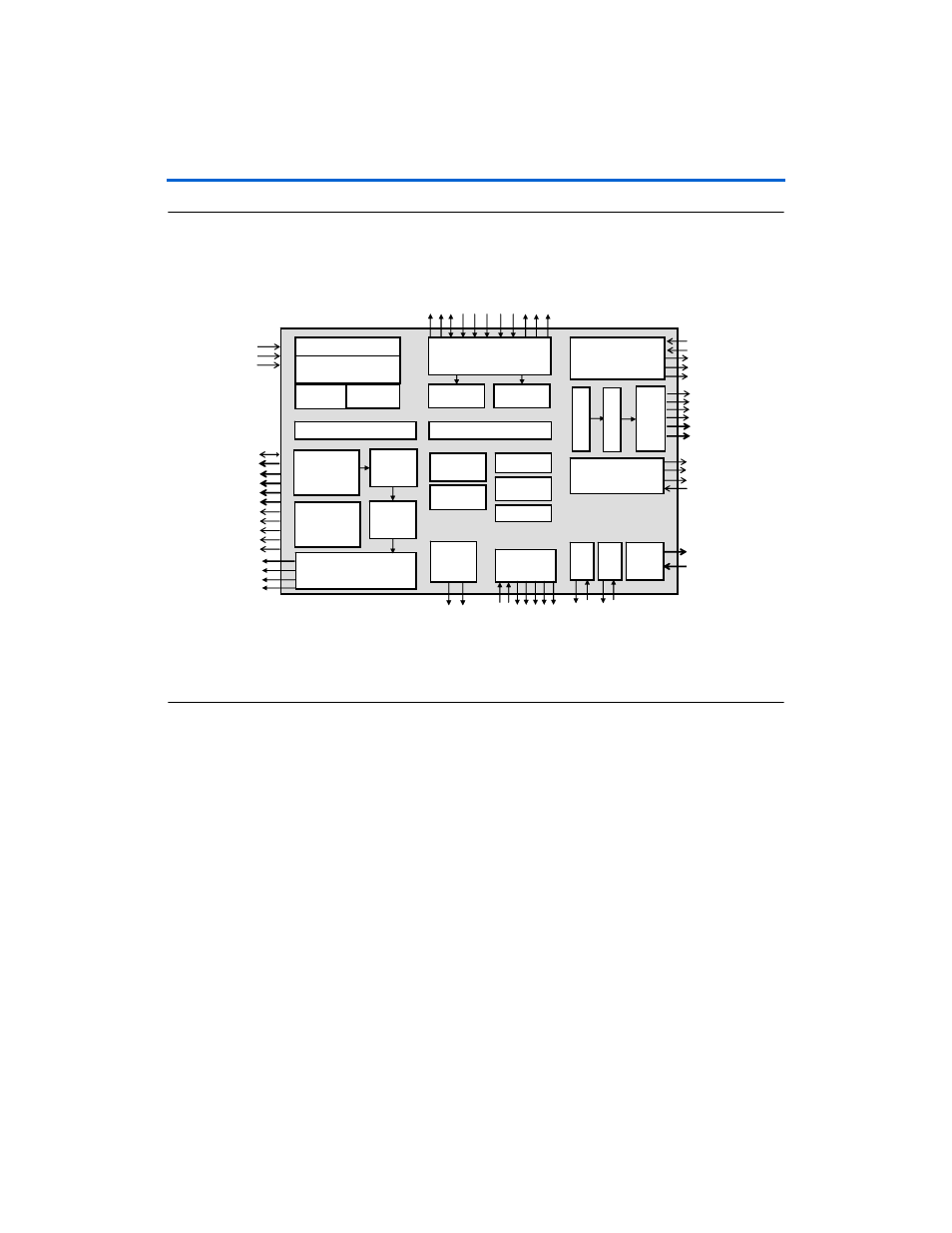

Figure 6–2. Nios II 3C120 Microprocessor with LCD Controller

Following is a summary of the processor system:

CPU Platform

The CPU platform consists of

■

Nios II/f cpu core

■

JTAG Debug Port

■

32KB Instruction Cache

■

32KB Data Cache

Memory Interfaces

■

DDR2 SDRAM Controller

●

Run time program and data memory

■

CFI Flash Controller

●

Stores FPGA configuration data

A[0-12]

BA[0-1]

DATA[0-15]

DM[0-1]

CAS

CS

OE

ODT

DATA[0-7]

CLKN

VSYNC

HSYNC

Nios II /f Core

DATA

CACHE

JTAG Debug Module

F

lash Int

e

rf

ace

SD/MMC Card

Interface

PLL

UA

RT

Touch

Panel

Interface

LED

Button

PIO

Performance

Counter

10/100 Ethernet MAC

DDR2 SDRAM

Controller 0

SG DMA

FIFO

System

Timer

High Res

Timer

System ID

TX SG DMA

RX SG DMA

Instruction

CACHE

DDR2 SDRAM

Controller 1

Slow Peripheral Bridge

Clock Crossing Bridge

Max II Configuration

Interface

Video Pipeline

Reset

CLK 125

CLK 50

DCLK

DATA0

CS_n

WE_n

OE_n

CLK, CLK #

DQS[0-1]

RAS

OE_n

ADDR[0-24]

DATA[0-31]

Reset

CE_n

WE_n

ADC Interface

CS

DCLK

DIN

DOUT

DEN

PE

NIRQ

DOUT

SDA

SCLK

R

E

SET

MD

C

MD

IO

R

X

_CLK

RX_COL

RX_CLK

RX_

D

[0

-3

]

RX_ER

R

TX

_

D

[0

-3

]

TX

_

C

L

K

TX

_

E

N

SD_CMD

SD_CLK

SD_DAT

SD_DAT3

LED[0-7]

BUTTON[0-3]

RX

D

TX

D

E

EPRO

M

SD

A

SCLK

Pi

pel

in

ed B

rid

ge

Tri

s

tat

e

B

ri

dge

Nios II 3C120 Microprocessor with LCD Controller

Nios II 3C120 Microprocessor with LCD Controller