Altera Cyclone III LS FPGA Development Board User Manual

Page 27

Chapter 2: Board Components

2–19

Configuration, Status, and Setup Elements

© October 2009 Altera Corporation

Cyclone III LS FPGA Development Board Reference Manual

lists the JTAG chain header switch component reference and

manufacturing information.

Anti-Tamper JTAG Select Header Switch

The anti-tamper JTAG select header switch (J12) is provided to disable the normal

JTAG chain, giving control of the FPGA JTAG signals to the MAX II CPLD EMP2210

System Controller GPIO signals. Note that when a shunt jumper is placed onto the

anti-tamper JTAG select header switch (J12), none of the devices in the JTAG chain can

be detected by the USB embedded blaster or the JTAG header. Refer to

for the JTAG chain functionality.

shows the anti-tamper JTAG select header switch controls and

descriptions.

lists the anti-tamper JTAG select header switch component reference and

manufacturing information.

LCD/HSMC Port B Data Select Header Switch

The LCD/HSMC port B data select header switch (J18) is provided to control data

multiplexing of the LCD and HSMB_D[65:75]signals to the Cyclone III LS device. If

the shunt is not placed on the jumper, the FPGA can control the LCD_HSMB_SEL

signal. The default value of this switch is a logic '1'.

shows the LCD/HSMC port B data select header switch controls and

descriptions.

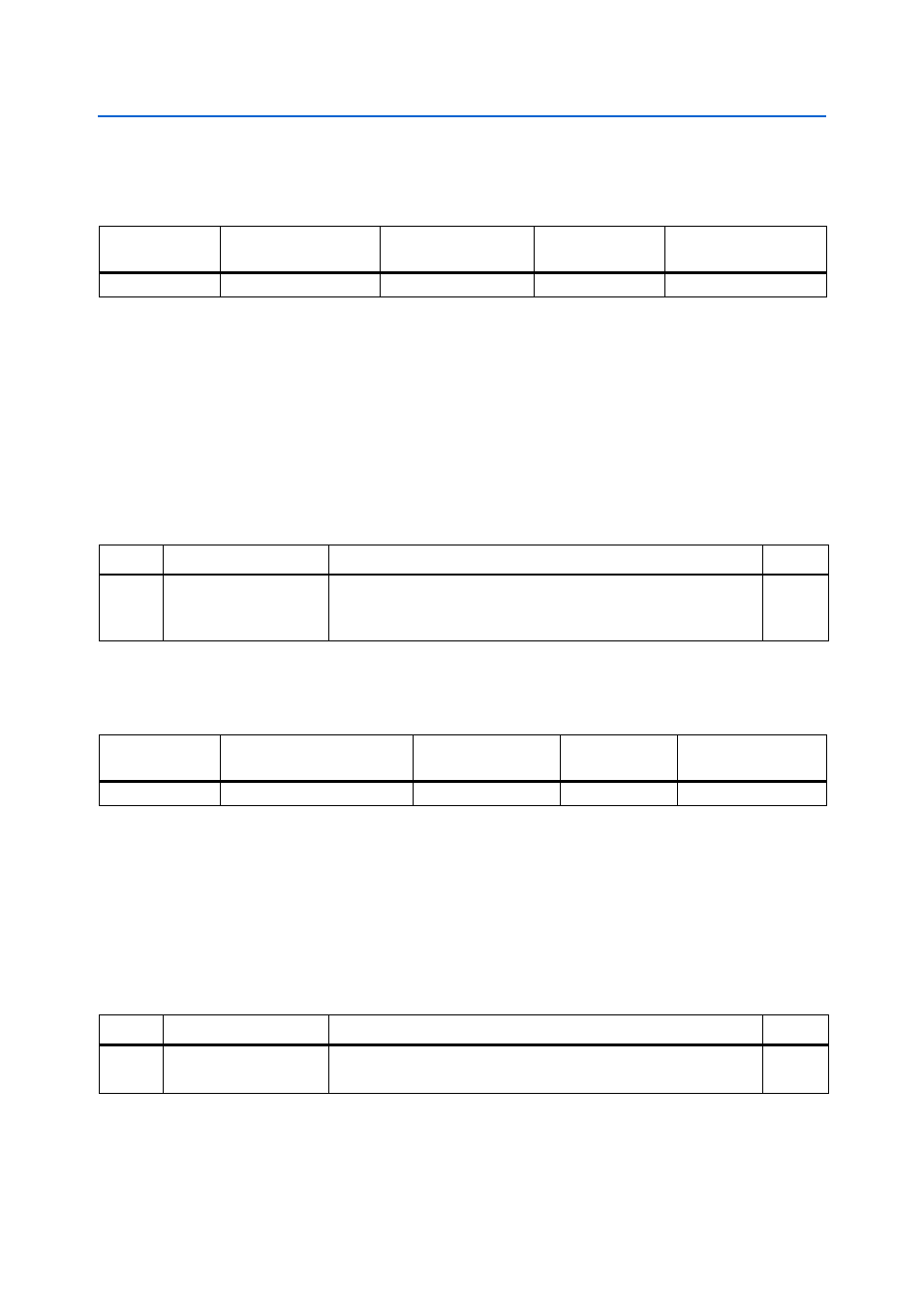

Table 2–14. JTAG Chain Header Switch Component Reference and Manufacturing Information

Board Reference

Device Description

Manufacturer

Manufacturer

Part Number

Manufacturer Website

J11

2x3 100 mil jumper

Samtec

TSW-103-07-L-D

Table 2–15. Anti-Tamper JTAG Select Header Switch Controls

Switch

Schematic Signal Name

Description

Default

1

JTAG_AT_SEL

ON: MAX II CPLD EPM2210 System Controller GPIO controls the FPGA

JTAG signals.

OFF: Normal JTAG chain functionality

OFF

Table 2–16. Anti-Tamper JTAG Select Header Switch Component Reference and Manufacturing Information

Board Reference

Description

Manufacturer

Manufacturer

Part Number

Manufacturer Website

J12

2x1 100 mil jumper

3M/ESD

929665-09-36-I

Table 2–17. LCD/HSMC Port B Data Select Header Switch Controls

Switch

Schematic Signal Name

Description

Default

1

LCD_HSMB_SEL

ON: FPGA control of the LCD signals.

OFF: FPGA control of the HSMB_D[65:75] signals.

OFF