Components and interfaces, 10/100/1000 ethernet, Components and interfaces –27 – Altera Cyclone III LS FPGA Development Board User Manual

Page 35: 10/100/1000 ethernet –27

Chapter 2: Board Components

2–27

Components and Interfaces

© October 2009 Altera Corporation

Cyclone III LS FPGA Development Board Reference Manual

1

The particular model used does not have a backlight and the LCD drive pin is not

connected.

lists the LCD component references and the manufacturing information.

Components and Interfaces

This section describes the development board's communication ports and interface

cards relative to the Cyclone III LS device. The development board supports the

following communication ports:

■

10/100/1000 Ethernet

■

HSMC

10/100/1000 Ethernet

A Marvell 88E1111 PHY device is used for 10/100/1000 BASE-T Ethernet connection.

The device is an auto-negotiating Ethernet PHY with an RGMII interface to the FPGA.

The MAC function must be provided in the FPGA for typical networking

applications. The Marvell 88E1111 PHY uses 2.5-V and 1.2-V power rails and requires

a 25-MHz reference clock driven from a dedicated oscillator. It interfaces to a Halo

Electronics HFJ11-1G02E model RJ45 with internal magnetics that can be used for

driving copper lines with Ethernet traffic.

5

R/W

H/L

H: Data read (module to MPU)

L: Data write (MPU to module)

6

E

H, H to L

Enable

7–14

DB0–DB7

H/L

Data bus, software selectable 4-bit or 8-bit mode

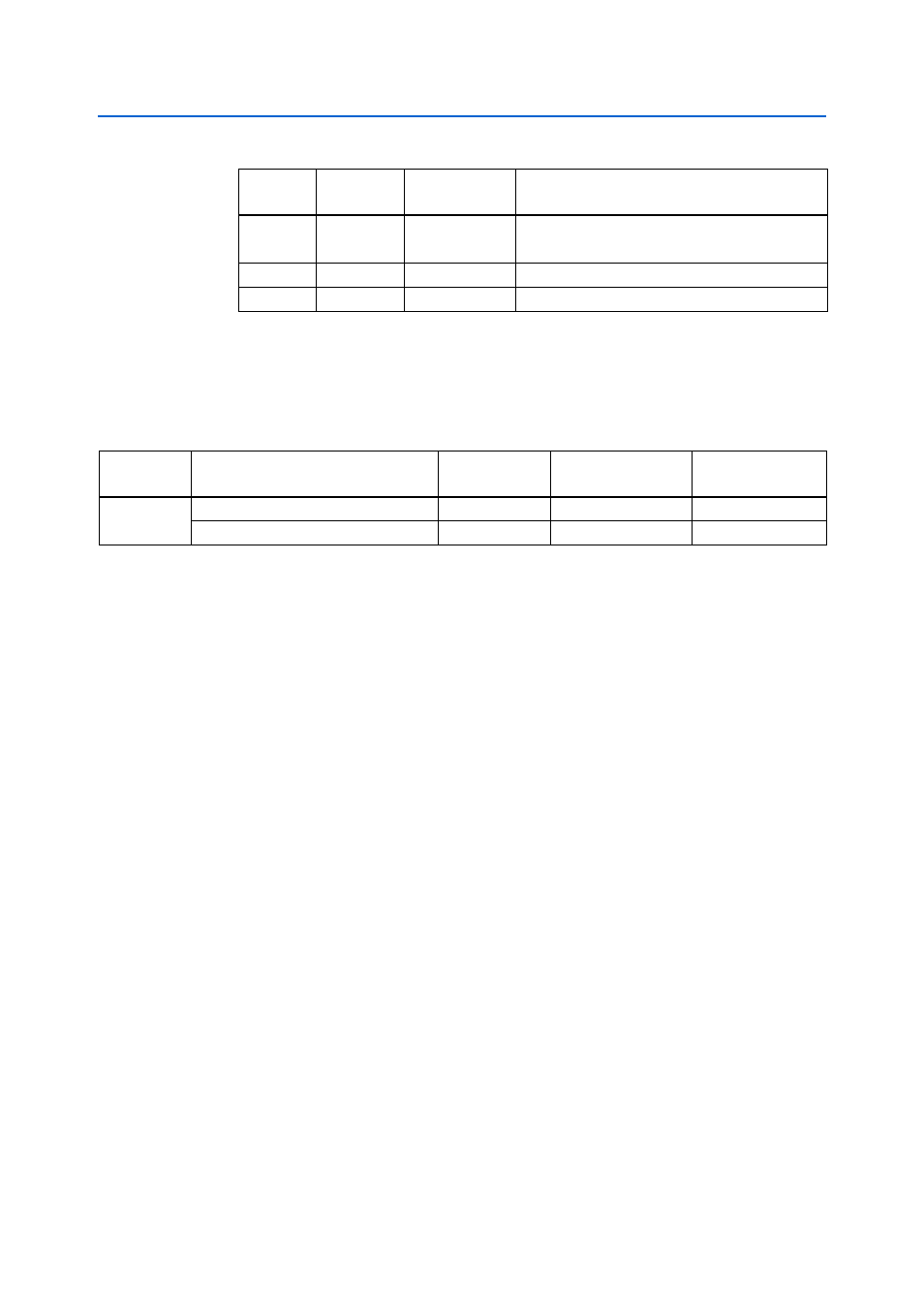

Table 2–30. LCD Pin Definitions and Functions (Part 2 of 2)

Pin

Number

Symbol

Level

Function

Table 2–31. LCD Component References and Manufacturing Information

Board

Reference

Description

Manufacturer

Manufacturer

Part Number

Manufacturer

Website

J19

2×7 pin, 100 mil, vertical header

Samtec

TSM-107-07-G-D

2×16 character display, 5×8 dot matrix

Lumex Inc.

LCM-S01602DSR/C