Flash, Flash –41 – Altera Cyclone III LS FPGA Development Board User Manual

Page 49

Chapter 2: Board Components

2–41

Memory

© October 2009 Altera Corporation

Cyclone III LS FPGA Development Board Reference Manual

lists the SSRAM component reference and manufacturing information.

Flash

The flash interface consists of a single synchronous flash memory device, providing

64 Mbyte with a 16-bit data bus. This device is part of the shared FSM bus which

connects to the flash memory, SRAM, and MAX II CPLD EPM2210 System Controller.

There are two 256-Mbyte die per package with A(25) low selecting the lower die and

A(25) high selecting the upper die. The parameter blocks are 32 K and main blocks are

128 K. The parameters of this device are located at both the top and bottom of the

address space.

This 16-bit data memory interface can sustain burst read operations at up to 52 MHz

for a throughput of 832 Mbps. The write performance is 125 µs for a single word and

440 µs for a 32-word buffer. The erase time is 400 ms for a 32 K parameter block and

1200 ms for a 128 K main block.

U14.A7

Byte write enable

SRAM_BWEn

2.5-V

AH8

U14.B5

Byte lane 0 write enable

SRAM_BWn0

AC12

U14.A5

Byte lane 1 write enable

SRAM_BWn1

AH11

U14.A4

Byte lane 2 write enable

SRAM_BWn2

AH4

U14.B4

Byte lane 3 write enable

SRAM_BWn3

AE22

U14.B3

Chip enable

SRAM_CE2

—

U14.A6

Chip enable

SRAM_CE3n

—

U14.A3

Chip enable

SRAM_CEn

AH10

U14.B6

Clock

SRAM_CLK

AG25

U14.N11

Data bus parity byte lane 0

SRAM_DQP0

AD19

U14.C11

Data bus parity byte lane 1

SRAM_DQP1

AF22

U14.C1

Data bus parity byte lane 2

SRAM_DQP2

AE8

U14.N1

Data bus parity byte lane 3

SRAM_DQP3

AE17

U14.B7

Global write enable

SRAM_GWn

AC19

U14.R1

Mode

SRAM_MODE

—

U14.B8

Output enable

SRAM_OEn

AB13

U14.H11

Sleep

SRAM_ZZ

AH14

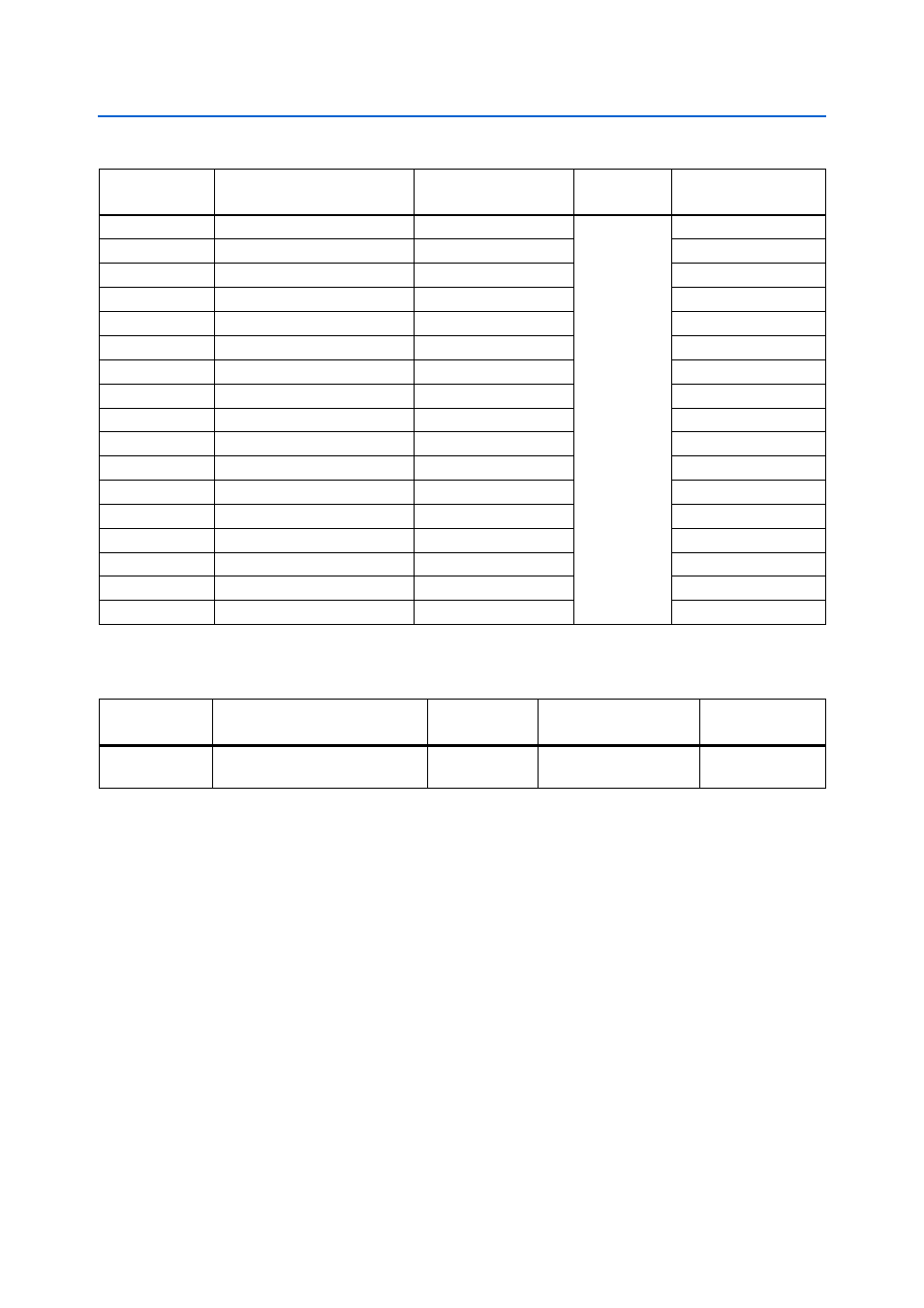

Table 2–40. SSRAM Pin Assignments, Schematic Signal Names, and Functions (Part 3 of 3)

Board Reference

Description

Schematic Signal Name

I/O Standard

Cyclone III LS Device

Pin Number

Table 2–41. SSRAM Component Reference and Manufacturing Information

Board Reference

Description

Manufacturer

Manufacturing

Part Number

Manufacturer

Website

U14

Standard Synchronous Pipelined

SCD, 512 K × 36, 200 MHz

ISSI Inc.

IS61VPS51236A-250B3