Altera Transceiver Signal Integrity Development Kit, Stratix IV GX Edition User Manual

Page 14

2–4

Chapter 2: Board Components

Board Overview

Transceiver Signal Integrity Development Kit,

November 2011

Altera Corporation

Stratix IV GX Edition Reference Manual

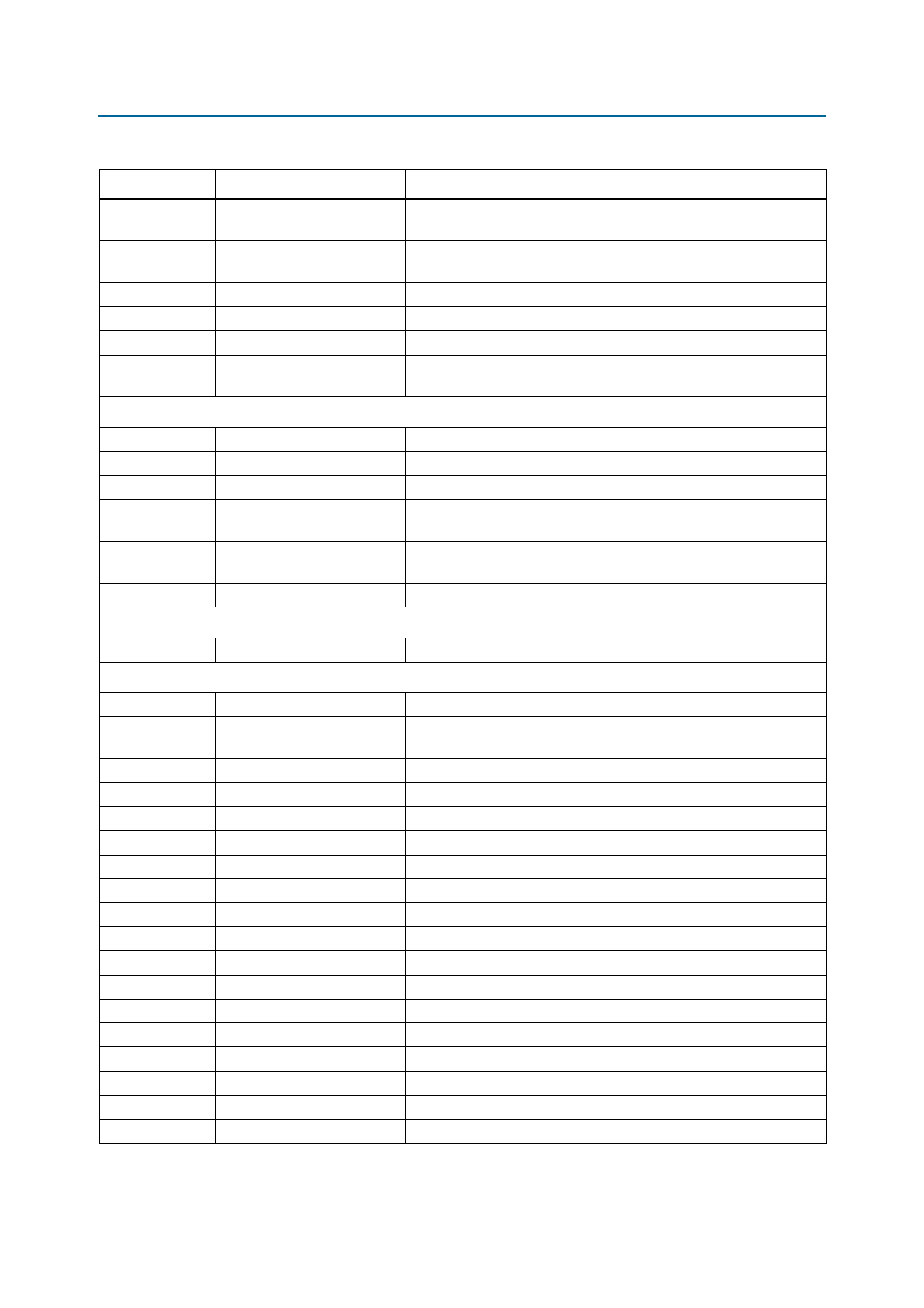

Y4, U23

100-MHz OSC and clock

buffer

100-MHz clock to FPGA transceivers.

Y5, U24

156.25-MHz OSC and clock

buffer

156.25-MHz clock to FPGA transceivers.

X1

6-MHz XTAL

XTAL for FTDI USB PHY Device.

Y1

24-MHz OSC

24-MHz oscillator for embedded USB-Blaster MAX II CPLD.

X3

25-MHz OSC

25-MHz oscillator for Marvell 88E1111 Ethernet PHY device.

X2, U21

25-MHz OSC and spread

spectrum clock buffer

25-MHz oscillator and spread spectrum clock buffer circuitry.

General User Input and Output

SW7

Bank of 8 user DIP switches

User DIP switches.

SW10–SW15

Bank of 6 user push buttons

User push buttons.

D8–D15

Bank of 8 user LEDs

User LEDs.

SW3–SW6

LCD control push buttons

Up, Down, Back, and Enter push buttons for implementing user LCD

menu/control.

J25

General purpose user I/O

header field

Four user I/Os brought out to a 0.1 in. header field.

J24

LCD interface header

Header for interfacing a 16 character × 2 line LCD.

Memory Devices

U39

Flash memory

512-Mb flash memory.

Components and Interfaces

CN1

USB Type-B connector

USB interface for embedded USB-Blaster.

U17

MAX II CPLD

Altera EPM7064AETC44 MAX II CPLD device for embedded

USB-Blaster circuitry.

J68

Ethernet RJ45 jack

Halo HFJ11-1G02E RJ45 Ethernet jack with integrated magnetic.

U40

10/100/1000 Ethernet PHY

Marvell 88E1111 triple speed Ethernet PHY.

J34, J36

GXB0 transmit channel 0

Transceiver GXB0 transmit channel 0 connected to SMA.

J30, J32

GXB0 receive channel 0

Transceiver GXB0 receive channel 0 connected to SMA.

J39, J41

GXB1 transmit channel 1

Transceiver GXB1 transmit channel 1 connected to SMA.

J43, J45

GXB1 transmit channel 2

Transceiver GXB1 transmit channel 2 connected to SMA.

J55, J57

GXB1 transmit channel 3

Transceiver GXB1 transmit channel 3 connected to SMA.

J59, J61

GXB1 transmit channel 4

Transceiver GXB1 transmit channel 4 connected to SMA.

J47, J49

GXB1 transmit channel 5

Transceiver GXB1 transmit channel 5 connected to SMA.

J51, J53

GXB1 transmit channel 6

Transceiver GXB1 transmit channel 6 connected to SMA.

J38, J40

GXB1 receive channel 1

Transceiver GXB1 receive channel 1 connected to SMA.

J42, J44

GXB1 receive channel 2

Transceiver GXB1 receive channel 2 connected to SMA.

J54, J56

GXB1 receive channel 3

Transceiver GXB1 receive channel 3 connected to SMA.

J58, J60

GXB1 receive channel 4

Transceiver GXB1 receive channel 4 connected to SMA.

J46, J48

GXB1 receive channel 5

Transceiver GXB1 receive channel 5 connected to SMA.

J50, J52

GXB1 receive channel 6

Transceiver GXB1 receive channel 6 connected to SMA.

Table 2–1. Stratix IV GX Transceiver Signal Integrity Development Board Components (Part 3 of 4)

(1)

Board Reference

Type

Description