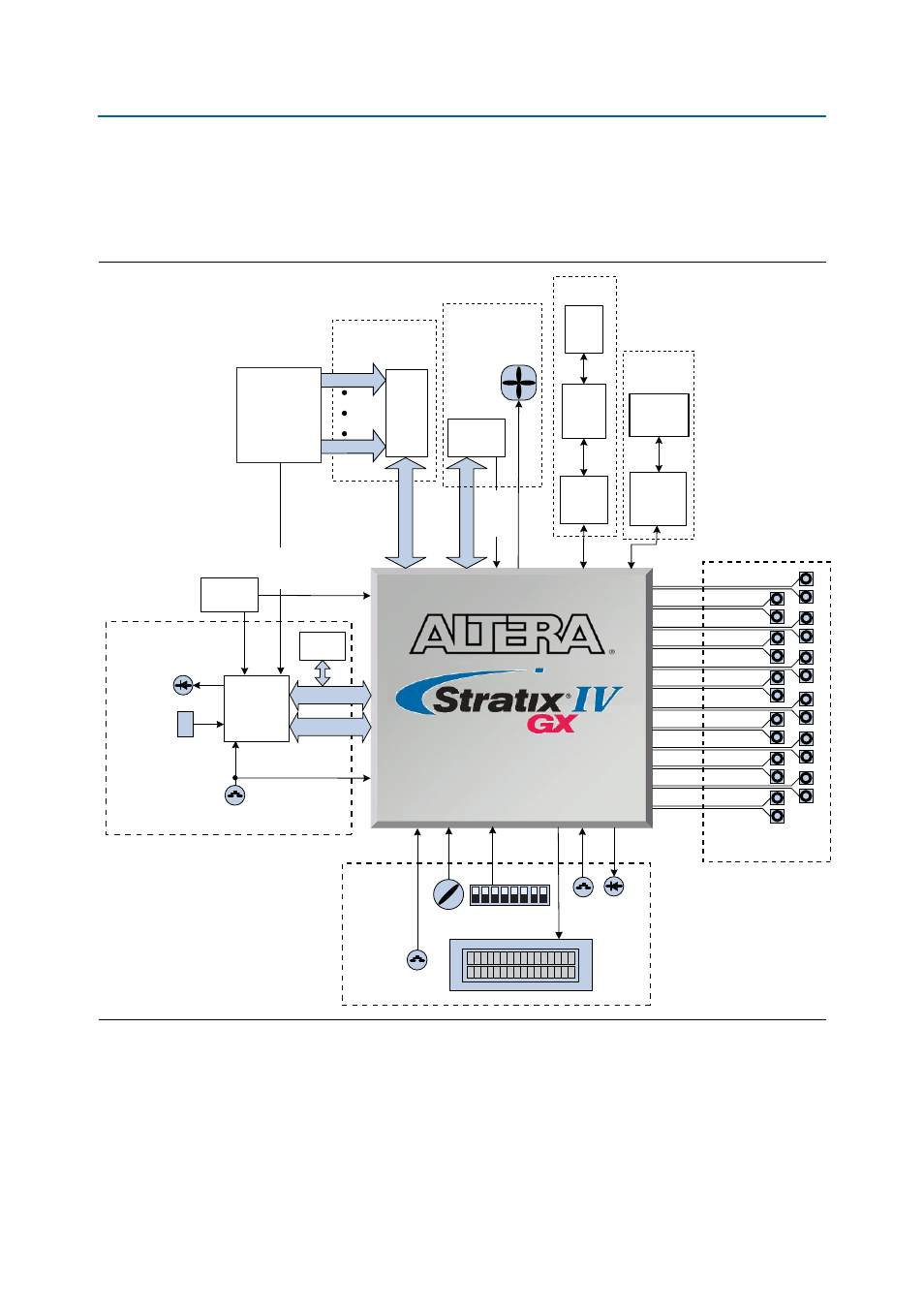

Development board block diagram, Development board block diagram –4 – Altera Transceiver Signal Integrity Development Kit, Stratix IV GX Edition User Manual

Page 8

1–4

Chapter 1: Overview

Development Board Block Diagram

Transceiver Signal Integrity Development Kit,

November 2011

Altera Corporation

Stratix IV GX Edition Reference Manual

Development Board Block Diagram

shows the block diagram of the Stratix IV GX transceiver signal integrity

board.

Figure 1–1. Stratix IV GX Transceiver Signal Integrity Board Block Diagram

LCD

Power

Measure

24-bit

ADC

ADC

TEMP

Dual Temp

Sensor

Temp

Measure

TDIODES

5-V FAN

USB-Blaster

USB

Type-B

Conn.

FTDI

745BL

USB

PHY

MAX

7064A

CPLD

10/100/1000

Ethernet

RJ45+

Magnetics

Marvell

88E1111

Ethernet

PHY

Pwrgood

FPP

Configuration

Clock

Circuitry

512-Mb

Flash

Configuration

Status LEDs

MAX II

EPM1270

CPLD

PGMSEL

Jumper

2 Reset

Push Buttons

Push Buttons

Switches

Displays

4 Menu

Push Buttons

Rotary

Switch

16 Char × 2 Line LCD

8 User DIP

6 User

Push

Buttons

8 User

LEDs

Transceivers Connected

to SMA Connectors

Flash

FPP Config

2-wire Ch1

Power

Circuitry

2-wire Ch8

EP4SGX230KF40