A. board revision history, Single-die flash version differences, Engineering silicon version differences – Altera Transceiver Signal Integrity Development Kit, Stratix IV GX Edition User Manual

Page 39: Appendix a. board revision history

November 2011

Altera Corporation

Transceiver Signal Integrity Development Kit,

Stratix IV GX Edition Reference Manual

A. Board Revision History

This appendix catalogs revisions to the Stratix IV GX transceiver signal integrity

development board.

lists the released versions of the Stratix IV GX transceiver signal integrity

development board.

Single-Die Flash Version Differences

The single-die flash version of the Stratix IV GX transceiver signal integrity

development board is created to replace the obsolete dual-die flash device with a

single-die flash device. The two flash devices are considered equivalent except for

some software routines used to access them because the single-die device has only

one CFI table whereas the duel-die device has two CFI tables.

To determine which flash your board is using, refer to the device part number

installed at U39. The single-die package is smaller than the dual-die version.

f

For more information about the flash change and its application, refer to the

.

Engineering Silicon Version Differences

The engineering silicon version of the Stratix IV GX transceiver signal integrity

development board is the initial release of the board. This section describes the

differences between the engineering silicon and production silicon versions of the

board.

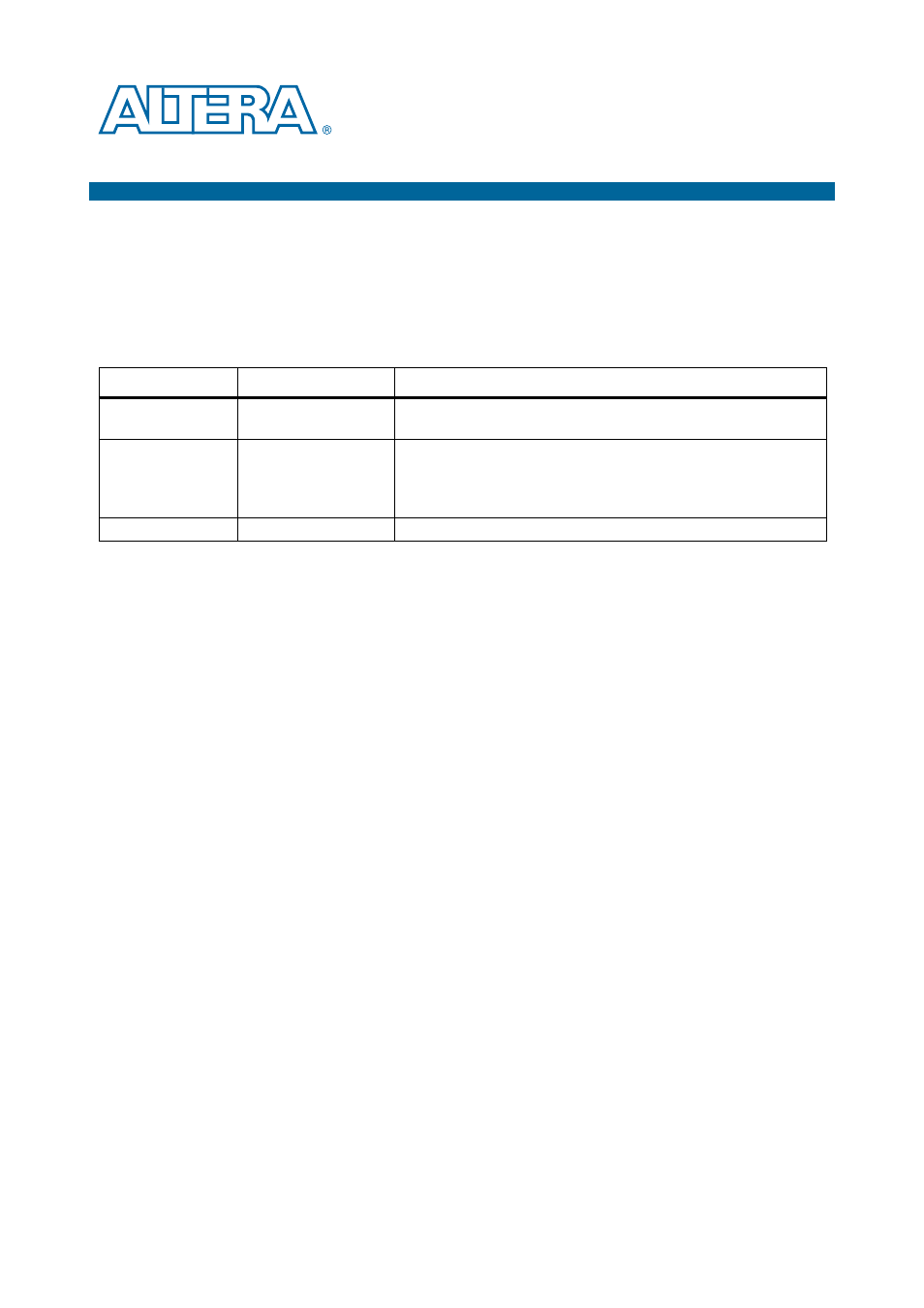

Table A–1. Stratix IV GX Transceiver Signal Integrity Development Board Revision History

Version

Release Date

Description

Single-die flash

November 2011

Replaced Intel dual-die 512-Mb flash PC48F4400P0VB00 with Numonyx

single-die flash PC28F512P30BF.

Production silicon

November 2009

Previously isolated power rails, VCCR and VCCT, have been combined

into a single VCCRT rail per the Stratix IV GX device pin connection

guidelines. Correspondingly, some associated board components are

removed from the production design.

Engineering silicon

February 2009

Initial release.