Altera QDRII SRAM Controller MegaCore Function User Manual

Page 27

Altera Corporation

MegaCore Version 9.1

2–17

November 2009

QDRII SRAM Controller MegaCore Function User Guide

Getting Started

1.

Create a directory in the <project directory>\testbench directory.

2.

Launch your simulation tool inside this directory and create the

following libraries:

●

<device name>_ver

●

auk_qdrii_lib

3.

Copy the <project directory>/simulation/<simulator name>_v.sdo file

into the compilation directory.

4.

into the appropriate library.

5.

Set the Tcl variable gRTL_DELAYS to 0, which tells the testbench not

to use the insert extra delays in the system, because these are

applied inside the gate level model. Configure your simulator to use

transport delays, a timestep of picoseconds, and to include the

auk_qdrii_lib and <device name>_ver library.

Simulating in Third-Party Simulation Tools Using NativeLink

You can perform a simulation in a third-party simulation tool from within

the Quartus II software, using NativeLink.

f

For more information on NativeLink, refer to the Simulating Altera IP

Using NativeLink chapter in volume 3 of the Quartus II Handbook.

To set up simulation in the Quartus II software using NativeLink, follow

these steps:

1.

Create a custom variation with an IP functional simulation model.

2.

Obtain and copy a memory model to a suitable location, for

example, the testbench directory.

1

Before running the simulation you may also need to edit the

testbench to match the chosen memory model.

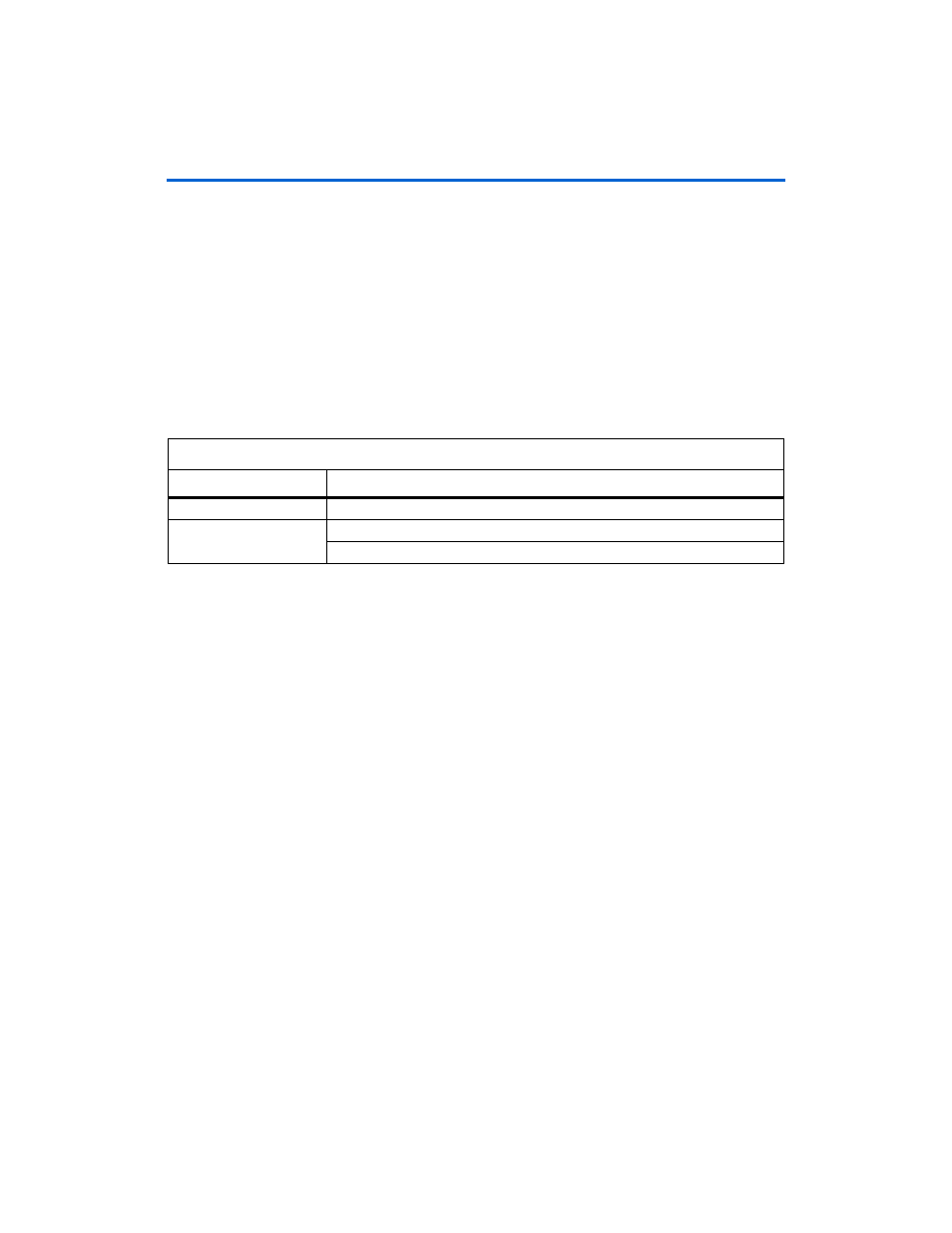

Table 2–5. Files to Compile—Verilog HDL Gate-Level Simulations

Library

Filename

<device name>_ver

<QUARTUS ROOTDIR>/eda/sim_lib/<device name>_atoms.v

auk_qdrii_lib

<project directory>/simulation/<simulator name>/<toplevel_name>.vo

<project directory>/testbench/<project name>_tb.v