A. programming the flash memory device, Cfi flash memory map, Appendix a. programming the flash memory device – Altera Cyclone V GT FPGA User Manual

Page 45

September 2014

Altera Corporation

Cyclone V GT FPGA Development Kit

User Guide

A. Programming the Flash Memory

Device

This appendix describes the preprogrammed contents of the common flash interface

(CFI) flash memory device and how to reprogram the user portions of flash memory.

As you develop your own project using the Altera tools, you can program the flash

memory device so that your own design loads from flash memory into the FPGA on

power up. The FPGA development board ships with the flash memory

preprogrammed with a default factory FPGA configuration. This configuration

allows you to run the Board Update Portal design example and the Board Test System

demonstration. There are several other factory software files written to the CFI flash

device to support the Board Update Portal. These software files were created using

the Nios II EDS, just as the hardware design was created using the Quartus II

software.

f

For more information about Altera development tools, refer to the

page of the Altera website.

CFI Flash Memory Map

shows the default memory contents of the 1-Gb CFI flash device. For the

Board Update Portal to run correctly and update designs in the user memory, this

memory map must not be altered.

c

Altera recommends that you do not overwrite the factory hardware and factory

software images unless you are an expert with the Altera tools. If you unintentionally

overwrite the factory hardware or factory software image, refer to

Flash Device to the Factory Settings” on page 4–6

.

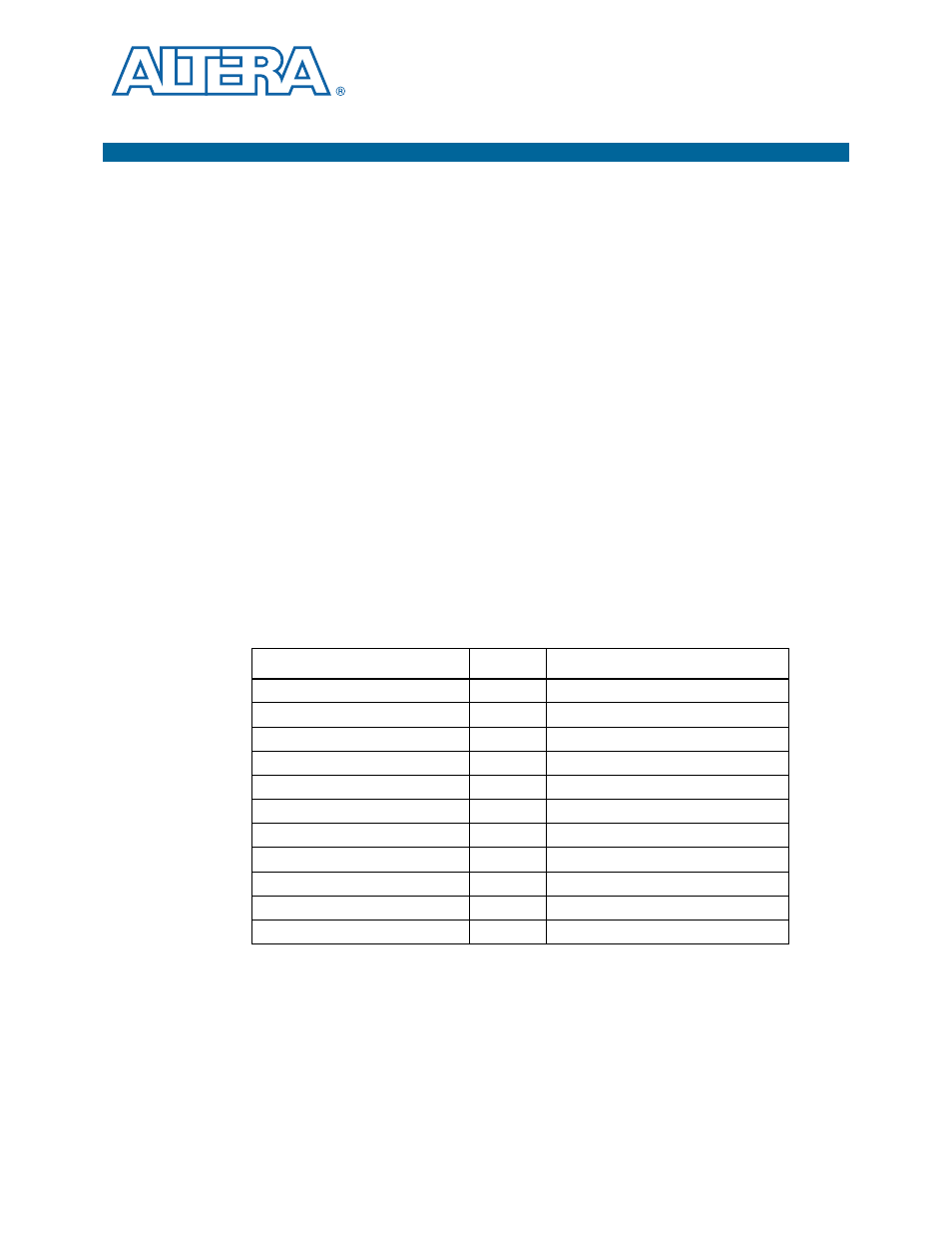

Table A–1. Byte Address Flash Memory Map

Block Description

KB Size

Address Range

Unused

128

0x07FE.0000 - 0x07FF.FFFF

User software

76,416

0x0354.0000 - 0x07FD.FFFF

Factory software

8,192

0x02D4.0000 - 0x0353.FFFF

zipfs (html, web content)

8,192

0x0254.0000 - 0x02D3.FFFF

User hardware 2

12,672

0x018E.0000 - 0x0253.FFFF

User hardware 1

12,672

0x00C8.0000 - 0x018D.FFFF

Factory hardware

12,672

0x0002.0000 - 0x00C7.FFFF

PFL option bits

32

0x0001.8000 - 0x0001.FFFF

Board information

32

0x0001.0000 - 0x0001.7FFF

Ethernet option bits

32

0x0000.8000 - 0x0000.FFFF

User design reset vector

32

0x0000.0000 - 0x0000.7FFF