Altera Stratix V GX FPGA Development Board User Manual

Page 46

2–38

Chapter 2: Board Components

Components and Interfaces

Stratix V GX FPGA Development Board

October 2014

Altera Corporation

Reference Manual

160

HSMA_PRSNTn

2.5-V

AW8

Presence detect signal

34

HSMA_SCL

2.5-V

AM29

Management serial clock line

33

HSMA_SDA

2.5-V

AL29

Management serial data line

50

HSMA_RX_D_N0

LVDS or 2.5-V

AW11

Data bus

56

HSMA_RX_D_N1

LVDS or 2.5-V

AU12

Data bus

62

HSMA_RX_D_N2

LVDS or 2.5-V

AR12

Data bus

68

HSMA_RX_D_N3

LVDS or 2.5-V

AK12

Data bus

74

HSMA_RX_D_N4

LVDS or 2.5-V

AJ12

Data bus

80

HSMA_RX_D_N5

LVDS or 2.5-V

AG10

Data bus

86

HSMA_RX_D_N6

LVDS or 2.5-V

AE12

Data bus

92

HSMA_RX_D_N7

LVDS or 2.5-V

AC10

Data bus

104

HSMA_RX_D_N8

LVDS or 2.5-V

R9

Data bus

110

HSMA_RX_D_N9

LVDS or 2.5-V

L9

Data bus

116

HSMA_RX_D_N10

LVDS or 2.5-V

L8

Data bus

122

HSMA_RX_D_N11

LVDS or 2.5-V

G11

Data bus

128

HSMA_RX_D_N12

LVDS or 2.5-V

F9

Data bus

134

HSMA_RX_D_N13

LVDS or 2.5-V

E8

Data bus

140

HSMA_RX_D_N14

LVDS or 2.5-V

E11

Data bus

146

HSMA_RX_D_N15

LVDS or 2.5-V

C9

Data bus

152

HSMA_RX_D_N16

LVDS or 2.5-V

A10

Data bus

48

HSMA_RX_D_P0

LVDS or 2.5-V

AV11

Data bus

54

HSMA_RX_D_P1

LVDS or 2.5-V

AT12

Data bus

60

HSMA_RX_D_P2

LVDS or 2.5-V

AR11

Data bus

66

HSMA_RX_D_P3

LVDS or 2.5-V

AL12

Data bus

72

HSMA_RX_D_P4

LVDS or 2.5-V

AH12

Data bus

78

HSMA_RX_D_P5

LVDS or 2.5-V

AF10

Data bus

84

HSMA_RX_D_P6

LVDS or 2.5-V

AD12

Data bus

90

HSMA_RX_D_P7

LVDS or 2.5-V

AB10

Data bus

102

HSMA_RX_D_P8

LVDS or 2.5-V

T9

Data bus

108

HSMA_RX_D_P9

LVDS or 2.5-V

M9

Data bus

114

HSMA_RX_D_P10

LVDS or 2.5-V

M8

Data bus

120

HSMA_RX_D_P11

LVDS or 2.5-V

H11

Data bus

126

HSMA_RX_D_P12

LVDS or 2.5-V

G10

Data bus

132

HSMA_RX_D_P13

LVDS or 2.5-V

F8

Data bus

138

HSMA_RX_D_P14

LVDS or 2.5-V

F11

Data bus

144

HSMA_RX_D_P15

LVDS or 2.5-V

C8

Data bus

150

HSMA_RX_D_P16

LVDS or 2.5-V

B10

Data bus

49

HSMA_TX_D_N0

LVDS or 2.5-V

AU11

Data bus

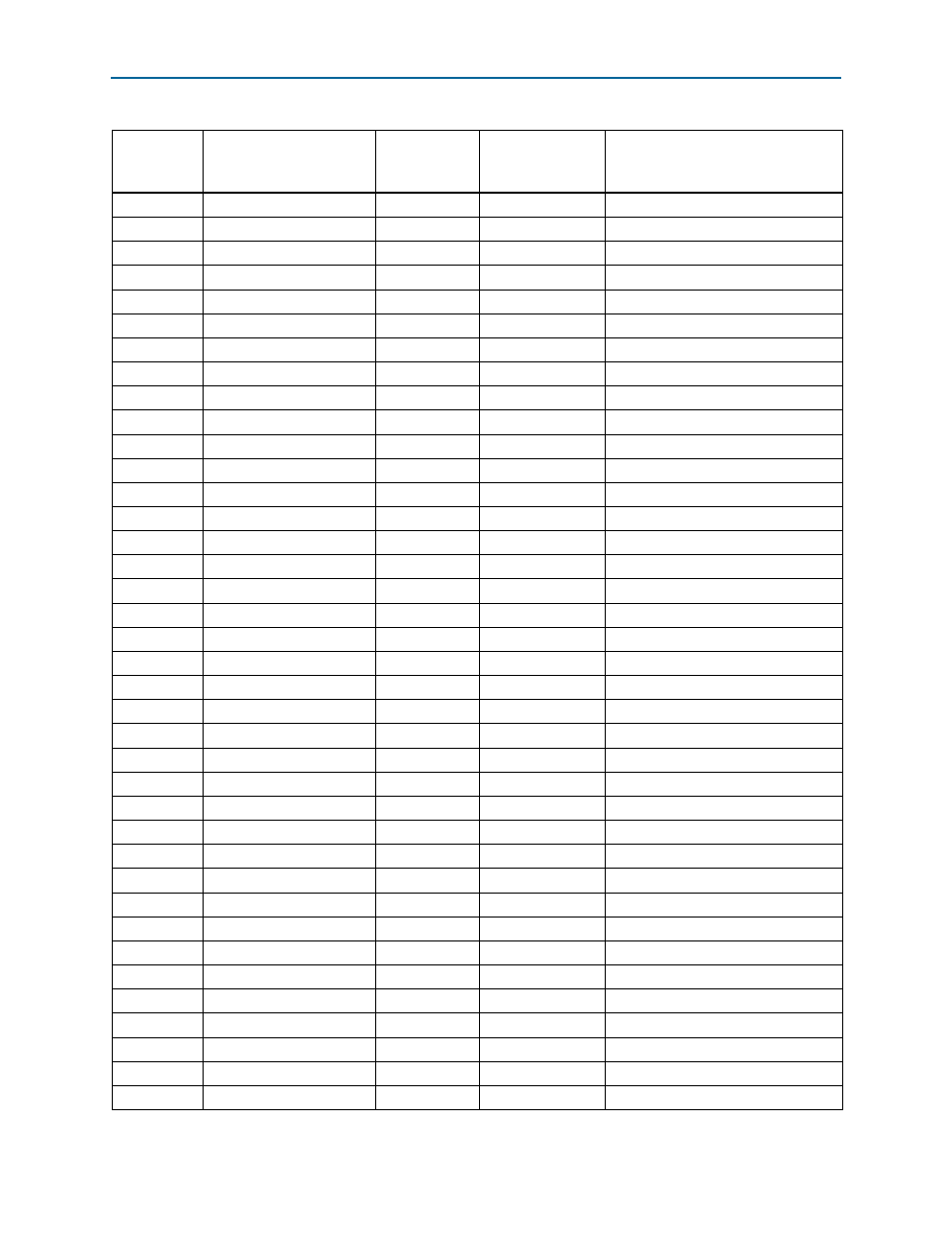

Table 2–40. HSMC Port A Pin Assignments, Schematic Signal Names, and Functions (Part 3 of 4)

Board

Reference

(J1)

Schematic Signal Name

I/O Standard

Stratix V GX FPGA

Device Pin

Number

Description