Configuration, status, and setup elements, Configuration, Status elements – Altera SDI HSMC User Manual

Page 13: Configuration, status, and setup elements –5, Configuration –5 status elements –5

Chapter 2: Board Components

2–5

Configuration, Status, and Setup Elements

© July 2009 Altera Corporation

Although there is only one clock generator PLL on the SDI HSMC, the board supports

two asynchronous clock systems when the host board supports two reference clock

input signals. You can use either a separate reference clock or an external reference as

input to the host board.

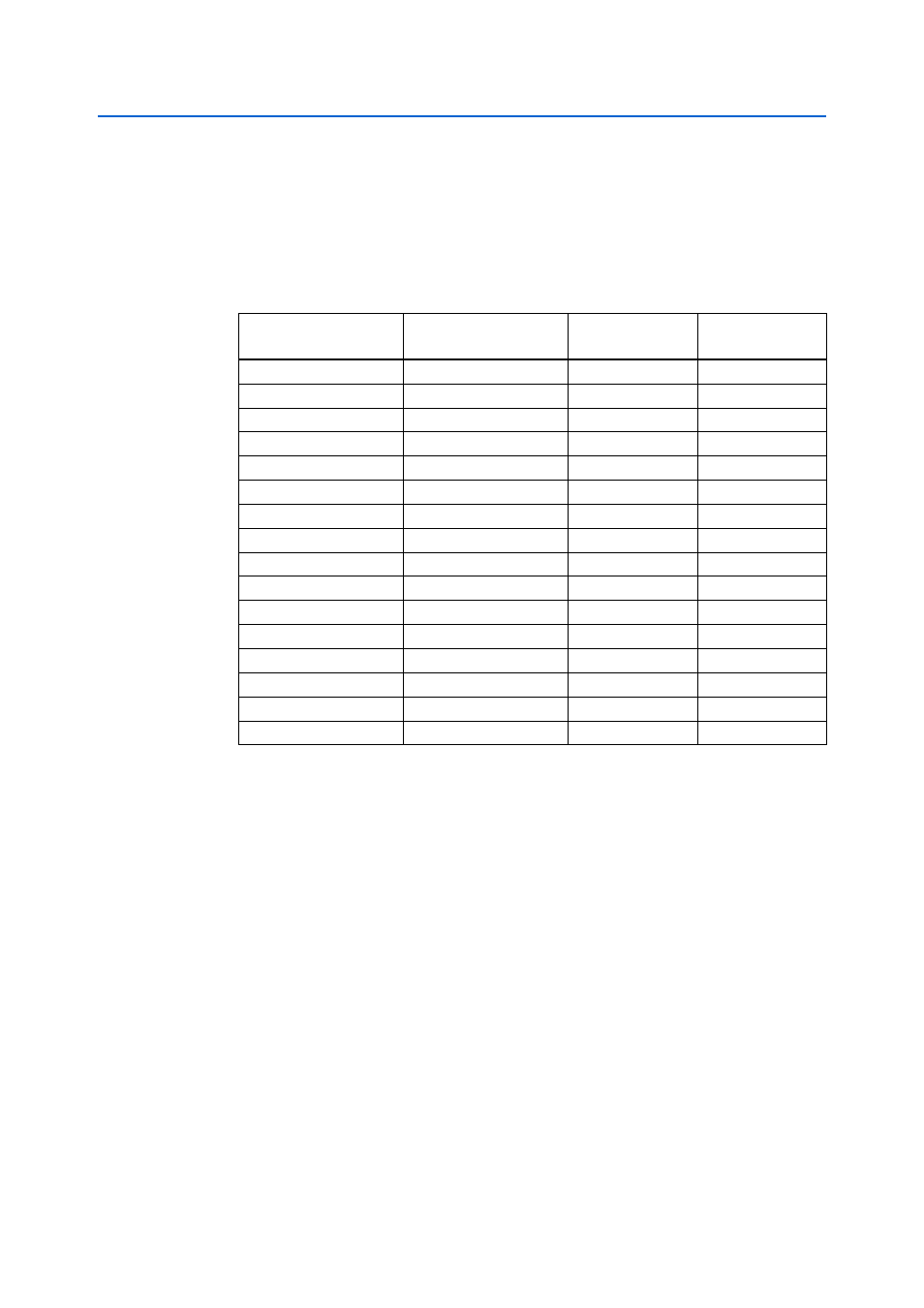

describes the features of the oversampling rate and associated clock

frequency for each supported audio sample rate.

Configuration, Status, and Setup Elements

This section describes board configuration, status, and setup.

Configuration

The standard jumper configuration has J4 (CD_MUTE2) and J6 (CD_MUTE1) installed.

Jumpers J5 (EQ_BYPASS2) and J7 (EQ_BYPASS1) can be driven from the host board.

These signals bypass the SDI cable equalizer when logic 1 is driven.

Status Elements

The development board includes status LEDs. This section describes the status

elements.

lists the LED board references and functional descriptions.

Table 2–3. AES3 Supported Bit Rates

Audio Sample Rate (kHz)

Bit Rate Clock (MHz)

(32 x 2 x 2)

Oversampling Rate

VCXO Frequency

24.0

3.0720

32

98.304

32

4.0960

24

98.304

44.1

5.6448

16

90.3168

48

6.1440

16

98.304

88.2

11.2896

8

90.3168

96

12.2880

8

98.304

176.4

22.5792

4

90.3168

192

24.5760

4

98.304

24.0

3.0720

40

122.8800

32

4.0960

30

122.8800

44.1

5.6448

20

112.8960

48

6.1440

20

122.8800

88.2

11.2896

10

112.8960

96

12.2880

10

122.8800

176.4

22.5792

5

112.8960

192

24.5760

5

122.8800